- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370702 > HSP3824VI (Harris Corporation) Direct Sequence Spread Spectrum Baseband Processor PDF資料下載

參數(shù)資料

| 型號(hào): | HSP3824VI |

| 廠商: | Harris Corporation |

| 元件分類: | 基帶處理器 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | 直接序列擴(kuò)頻基帶處理器 |

| 文件頁數(shù): | 5/41頁 |

| 文件大?。?/td> | 276K |

| 代理商: | HSP3824VI |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

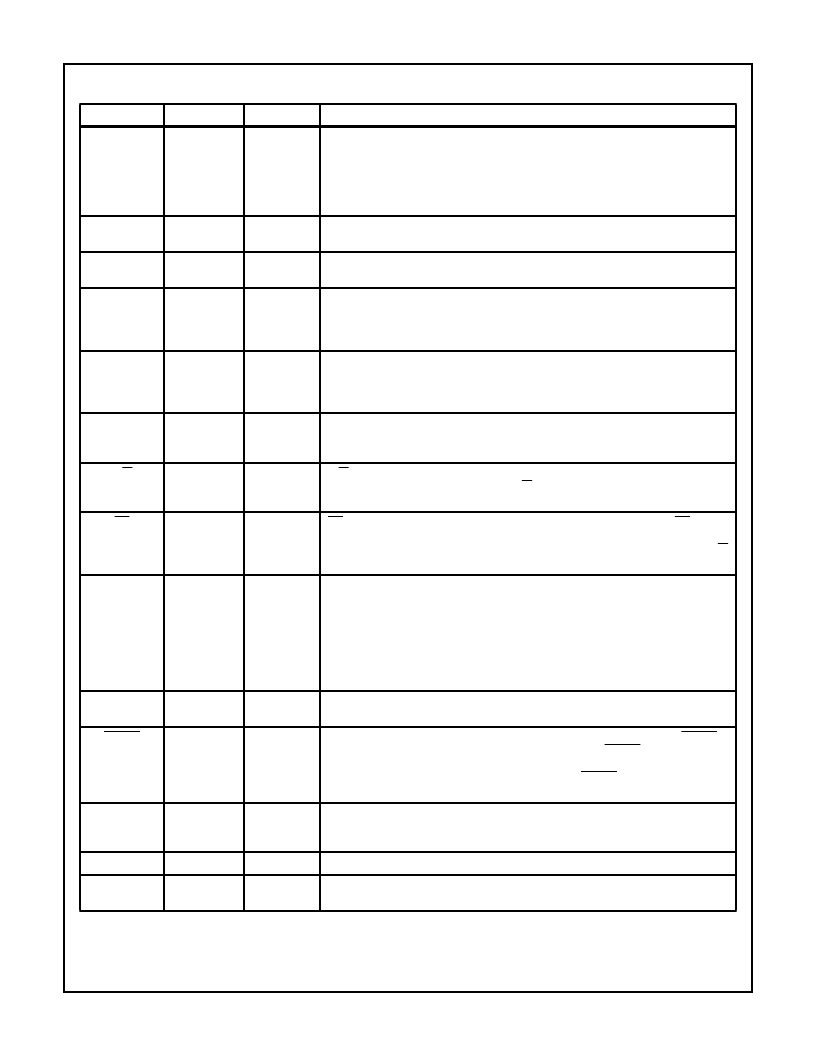

5

HSP3824

MD_RDY

34

O

MD_RDY is an output signal to the network processor, indicating a data packet is

ready to be transferred to the processor. MD_RDY is an active high signal and it

envelopes the data transfer over the RXD serial bus. MD_RDY returns to its inactive

state when there is no more receiver data, when the programmable data length

counter reaches its value or when the link has been interrupted. MD_RDY remains

inactive during preamble synchronization.

RX_PE

33

I

When active, receiver is configured to be operational, otherwise receiver is in standby

mode. This is an active high input signal.

ANTSEL

27

O

The antenna select signal changes state as the receiver switches from antenna to

antenna during the acquisition process in the antenna diversity mode.

SD

25

I/O

SD is a serial bi-directional data bus which is used to transfer address and data to/from

the internal registers. The bit ordering of an 8-bit word is MSB first. The first 8 bits

during transfers indicate the register address immediately followed by 8 more bits

representing the data that needs to be written or read at that register.

SCLK

24

I

SCLK is the clock for the SD serial bus.The data on SD is clocked at the rising edge.

SCLK is an input clock and it is asynchronous to the internal master clock (MCLK)The

maximum rate of this clock is 10MHz or the master clock frequency, whichever is

lower.

AS

23

I

AS is an address strobe used to envelope the Address or the data on SD.

Logic 1 = envelopes the address bits.

Logic 0 = envelopes the data bits.

R/W

8

I

R/W is an input to the HSP3824 used to change the direction of the SD bus when

reading or writing data on the SD bus. R/W must be set up prior to the rising edge of

SCLK. A high level indicates read while a low level is a write.

CS

9

I

CS is a Chip select for the device to activate the serial control port.The CS doesn’t

impact any of the other interface ports and signals, i.e. the TX or RX ports and

interface signals. This is an active low signal. When inactive SD, SCLK, AS and R/W

become “don’t care” signals.

TEST 0-7

37, 38, 39,

40, 43, 44,

45, 46

O

This is a data port that can be programmed to bring out internal signals or data for

monitoring. This data includes: Correlator phase and magnitude, NCO frequency

offset estimate, and signal quality estimates. Some of the discrete signals available

include: Carrier Sense (CRS), which becomes active when initial PN acquisition has

been declared. Energy Detect (ED) which becomes active when the integrated RSSI

value exceeds the programmable threshold. Both ED and CRS are active high

signals.These bits are primarily reserved by the manufacturer for testing. A further

description of the test port is given at the appropriate section of this data sheet.

TEST_CK

1

O

This is the clock that is used in conjunction with the data that is being output from the

test bus (TEST 0-7).

RESET

28

I

Master reset for device. When active TX and RX functions are disabled. If RESET is

kept low the HSP3824 goes into the power standby mode. RESET does not alter any

of the configuration register values nor it presets any of the registers into default

values. Device requires programming upon power-up. RESET must be inactive during

programming of the device.

MCLK

30

I

Master Clock for device. The maximum frequency of this clock is 44MHz. This is used

internally to generate all other internal necessary clocks and is divided by 1, 2, 4, or 8

for the transceiver clocks.

I

OUT

48

O

TX Spread baseband I digital output data. Data is output at the programmed chip rate.

Q

OUT

47

O

TX Spread baseband Q digital output data. Data is output at the programmed chip

rate.

NOTE: Total of 48 pins; ALL pins are used.

Pin Description

(Continued)

NAME

PIN

TYPE I/O

DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSR101 | Silicon Schottky Barrier Diode for Various detector, High speed switching(用于多種檢波和高速開關(guān)的肖特基勢(shì)壘二極管) |

| HSRD1056RH165S | Converter IC |

| HSRD1056RH169H | Converter IC |

| HSRD1056RH169S | Converter IC |

| HSRD1056RH240H | Converter IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP3824VI96S5001 | 制造商:Harris Corporation 功能描述: |

| HSP40223221 | 制造商:PARMAR 功能描述:BALLAST HPS/MH 400W 制造商:PARMAR 功能描述:BALLAST, HPS/MH, 400W |

| HSP4070C | 制造商:JLWORLD 制造商全稱:JLWORLD 功能描述:SPEAKER SOUND GENERATORS |

| HSP40G-8 | 制造商:JLWORLD 制造商全稱:JLWORLD 功能描述:SPEAKER SOUND GENERATORS |

| HSP43124 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Serial I/O Filter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。