- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370702 > HSP3824VI (Harris Corporation) Direct Sequence Spread Spectrum Baseband Processor PDF資料下載

參數(shù)資料

| 型號: | HSP3824VI |

| 廠商: | Harris Corporation |

| 元件分類: | 基帶處理器 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | 直接序列擴(kuò)頻基帶處理器 |

| 文件頁數(shù): | 4/41頁 |

| 文件大小: | 276K |

| 代理商: | HSP3824VI |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

4

HSP3824

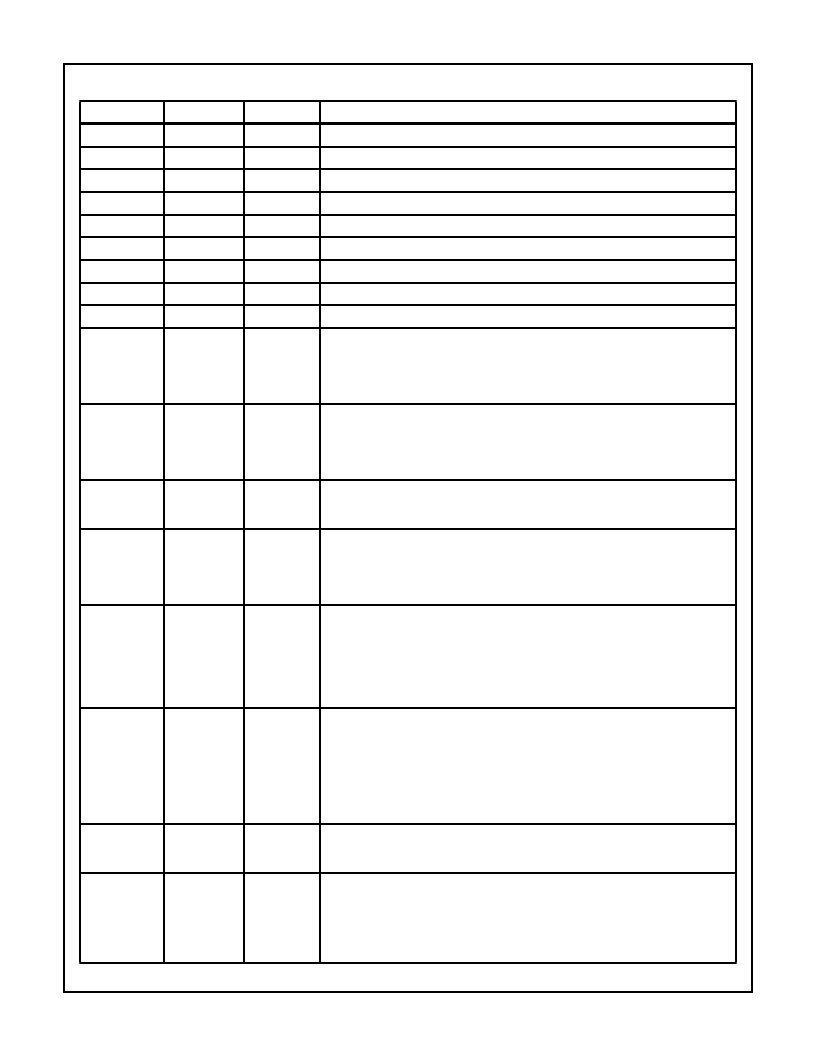

Pin Description

NAME

PIN

TYPE I/O

DESCRIPTION

V

DD

(Analog)

10, 18, 20

Power

DC power supply 2.7V - 5.5V

V

DD

(Digital)

7, 21, 29, 42

Power

DC power supply 2.7V - 5.5V

GND (Analog)

11, 15, 19

Ground

DC power supply 2.7V - 5.5V, ground.

GND (Digital)

6, 22, 31, 41

Ground

DC power supply 2.7V - 5.5V, ground.

V

REFN

17

I

“Negative” voltage reference for ADC’s (I and Q) [Relative to V

REFP

]

V

REFP

16

I

“Positive” voltage reference for ADC’s (I, Q and RSSI)

I

IN

12

I

Analog input to the internal 3-bit A/D of the In-phase received data.

Q

IN

13

I

Analog input to the internal 3-bit A/D of the Quadrature received data.

RSSI

14

I

Receive Signal Strength Indicator Analog input.

A/D_CAL

26

O

This signal is used internally as part of the I and Q ADC calibration circuit. When the

ADC calibration circuit is active, the voltage references of the ADCs are adjusted to

maintain the outputs of the ADCs in their optimum range. A logic 1 on this pin indicates

that one or both of the ADC outputs are at their full scale value. This signal can be

integrated externally as a control voltage for an external AGC.

TX_PE

2

I

When active, the transmitter is configured to be operational, otherwise the transmitter

is in standby mode. TX_PE is an input from the external Media Access Controller

(MAC) or network processor to the HSP3824. The rising edge of TX_PE will start the

internal transmit state machine and the falling edge will inhibit the state machine.

TX_PE envelopes the transmit data.

TXD

3

I

TXD is an input, used to transfer serial Data or Preamble/Header information bits from

the MAC or network processor to the HSP3824. The data is received serially with the

LSB first. The data is clocked in the HSP3824 at the falling edge of TXCLK.

TXCLK

4

O

TXCLK is a clock output used to receive the data on the TXD from the MAC or network

processor to the HSP3824, synchronously. Transmit data on the TXD bus is clocked

into the HSP3824 on the falling edge. The clocking edge is also programmable to be

on either phase of the clock. The rate of the clock will be depending upon the

modulation type and data rate that is programmed in the signalling field of the header.

TX_RDY

5

O

When the HSP3824 is configured to generate the preamble and Header information

internally, TX_RDY is an output to the external network processor indicating that

Preamble and Header information has been generated and that the HSP3824 is ready

to receive the data packet from the network processor over the TXD serial bus. The

TX_RDY returns to the inactive state when the TX_PE goes inactive indicating the end

of the data transmission. TX_RDY is an active high signal. This signal is meaningful

only when the HSP3824 generates its own preamble.

CCA

32

O

Clear Channel Assessment (CCA) is an output used to signal that the channel is clear

to transmit. The CCA algorithm is user programmable and makes its decision as a

function of RSSI, Energy detect (ED), Carrier Sense (CRS) and the CCA watch dog

timer. The CCA algorithm and its programmable features are described in the data

sheet.

Logic 0 = Channel is clear to transmit.

Logic 1 = Channel is NOT clear to transmit (busy).

NOTE: This polarity is programmable and can be inverted.

RXD

35

O

RXD is an output to the external network processor transferring demodulated Header

information and data in a serial format. The data is sent serially with the LSB first. The

data is frame aligned with MD_RDY.

RXCLK

36

O

RXCLK is the clock output bit clock. This clock is used to transfer Header information

and data through the RXD serial bus to the network processor. This clock reflects the

bit rate in use.RXCLK will be held to a logic “0” state during the acquisition process.

RXCLK becomes active when the HSP3824 enters in the data mode. This occurs once

bit sync is declared and a valid signal quality estimate is made, when comparing the

programmed signal quality thresholds.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSR101 | Silicon Schottky Barrier Diode for Various detector, High speed switching(用于多種檢波和高速開關(guān)的肖特基勢壘二極管) |

| HSRD1056RH165S | Converter IC |

| HSRD1056RH169H | Converter IC |

| HSRD1056RH169S | Converter IC |

| HSRD1056RH240H | Converter IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP3824VI96S5001 | 制造商:Harris Corporation 功能描述: |

| HSP40223221 | 制造商:PARMAR 功能描述:BALLAST HPS/MH 400W 制造商:PARMAR 功能描述:BALLAST, HPS/MH, 400W |

| HSP4070C | 制造商:JLWORLD 制造商全稱:JLWORLD 功能描述:SPEAKER SOUND GENERATORS |

| HSP40G-8 | 制造商:JLWORLD 制造商全稱:JLWORLD 功能描述:SPEAKER SOUND GENERATORS |

| HSP43124 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Serial I/O Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。