- 您現(xiàn)在的位置:買賣IC網 > PDF目錄67681 > IBM21P100BGB PCI BUS CONTROLLER, PBGA304 PDF資料下載

參數資料

| 型號: | IBM21P100BGB |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA304 |

| 封裝: | 31 X 31 MM, HEAT SINK, PLASTIC, BGA-304 |

| 文件頁數: | 125/140頁 |

| 文件大小: | 2032K |

| 代理商: | IBM21P100BGB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁當前第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁

IBM21P100BGB

IBM 133 PCI-X Bridge R1.1

ppb11_pcix_regs.fm.03

July 9, 2001

Configuration Registers

Page 77 of 131

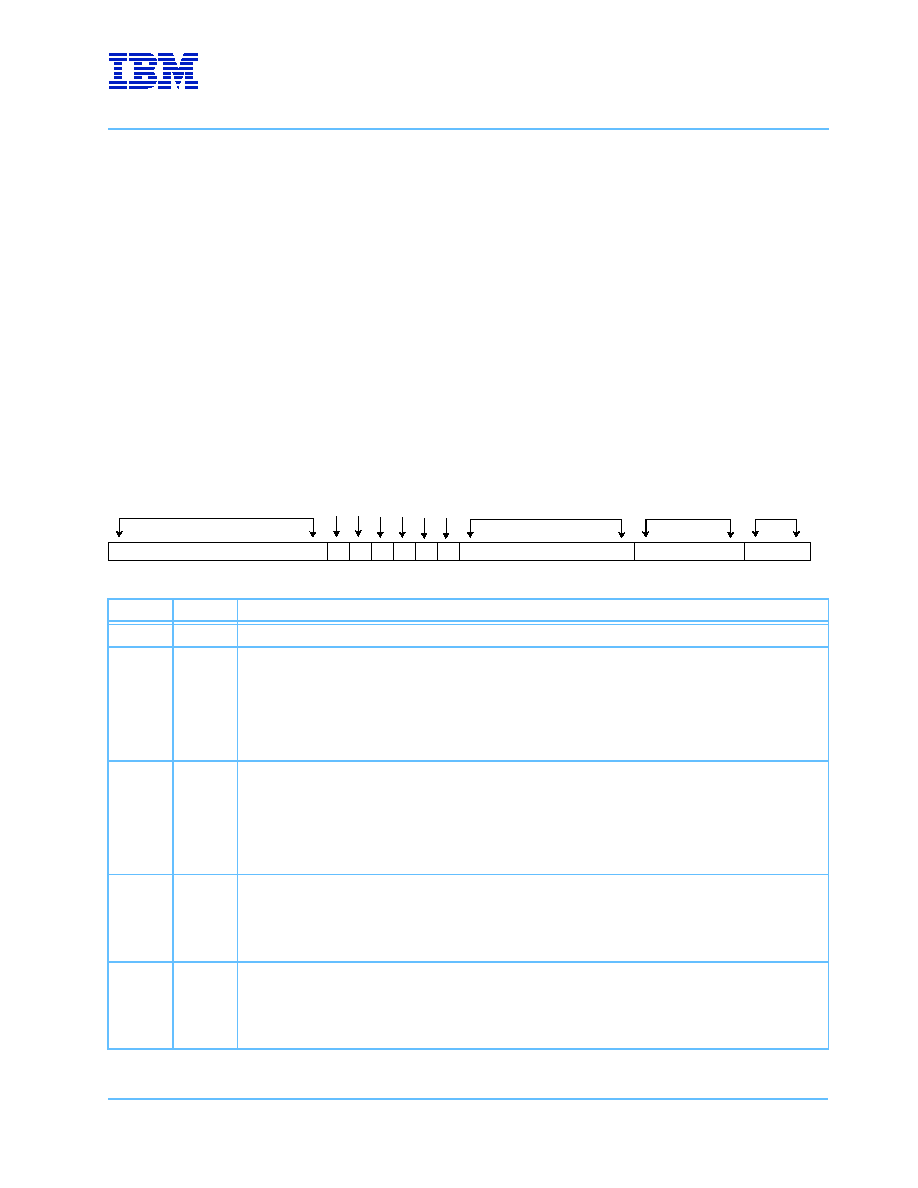

5.2.5.20 PCI-X Bridge Status Register

The PCI-X Bridge Status register identifies the capabilities and current operating mode of the bridge on its

primary bus as listed in the following table.

Address Offset

x‘84’

Access

See individual bit descriptions. Reads to this register behave normally. Writes are

slightly different in that bits can be reset, but not set. A bit is reset whenever the

register is written, and the data in the corresponding bit location is a ‘1’.

Reset Value

x‘0003 00F8’

Res

e

rv

ed

Split

Reques

t

D

elayed

S

p

lit

Com

p

le

ti

on

Ov

errun

Unexpec

te

d

S

plit

Com

p

let

ion

Split

Com

p

le

ti

on

D

is

c

arded

133

MHz

C

apable

64-bit

D

ev

ic

e

Bus

N

um

ber

D

e

vi

ce

N

u

m

ber

F

unct

ion

Num

ber

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

98

76543210

Bit(s)

Access

Field Name and Description

31:22

RO

Reserved

21

RW

Split Request Delayed

This bit is set any time the bridge has a request to forward a transaction to the primary bus, but cannot because

there is not enough room within the limit specified in the Split Transaction Commitment Limit field in the

Upstream Split Transaction Control register. It is used by algorithms that optimize the setting of the upstream

Split Transaction Commitment Limit register.

0

the bridge has not delayed a Split Request.

1

the bridge has delayed a Split Request.

20

RW

Split Completion Overrun

This bit is set if the bridge terminates a Split Completion on the primary bus with Retry or Disconnect at Next

ADB because the bridge buffers are full. It is used by algorithms that optimize the setting of the upstream Split

Transaction Commitment Limit register.

0

the bridge has accepted all Split Completions

1

the bridge has terminated a Split Completion with Retry or Disconnect at Next ADB because the

bridge buffers were full.

19

RW

Unexpected Split Completion

This bit is set if an unexpected Split Completion with a Requester ID equal to the bridge’s primary bus number,

device number, and function number is received on the bridge’s primary interface.

0

no unexpected Split Completion has been received

1

an unexpected Split Completion has been received

18

RW

Split Completion Discarded

This bit is set if the bridge discards a Split Completion moving toward the primary bus because the requester

would not accept it.

0

no Split Completion has been discarded

1

a Split Completion has been discarded

相關PDF資料 |

PDF描述 |

|---|---|

| IBM21P100BGC | PCI BUS CONTROLLER, PBGA304 |

| IBM25403GCX-3JC76C2 | RISC PROCESSOR, PQFP16 |

| IBM25405GP-3BA200C2 | RISC PROCESSOR, PBGA456 |

| IBM25EMPPC603EFG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PQFP240 |

| IBM25EMPPC603EBG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IBM24L5086 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM25403GCX-3BC80C2 | 制造商:IBM 功能描述:RISC PROCESSOR, 160 Pin Plastic BGA |

| IBM25403GCX-3JC50C2 | 制造商:IBM 功能描述:403GCX-3JC50C2 |

| IBM25403GCX-3JC66C2 | 制造商:IBM 功能描述: |

| IBM25403GCX3JC76C2 | 制造商:IBM 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。