- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄67681 > IBM21P100BGC PCI BUS CONTROLLER, PBGA304 PDF資料下載

參數(shù)資料

| 型號(hào): | IBM21P100BGC |

| 元件分類(lèi): | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA304 |

| 封裝: | 31 X 31 MM, PLASTIC, BGA-304 |

| 文件頁(yè)數(shù): | 5/144頁(yè) |

| 文件大?。?/td> | 5197K |

| 代理商: | IBM21P100BGC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)

IBM21P100BGC

IBM 133 PCI-X Bridge R2.0

Clocking and Reset

Page 102 of 144

ppb20_clock_reset.fm.01

October 15, 2001

tie-up the signal, this may be useful for fixed frequency applications with simple clock generators or oscilla-

tors. A third possibility may be to use a ‘power good’ indicator, if the proper stability assurances can be made.

Other ways to provide the S_CLK_STABLE input signal may also be possible.

The S_CLK_STABLE input provides another measure of control for cases where the secondary bus mode

and clock frequency could vary from reset to reset, as in motherboard applications with pluggable slots. In

these applications the external clock generation circuitry will need to adapt to the changes along with the

bridge. If the S_CLK_STABLE signal is initially held low during reset, the bridge will not control the

S_PCIXCAP network and the clock generation circuitry is free to do its own mode and frequency determina-

tion sequence. The clock frequency may be adjusted based on the number of populated slots, determined by

the PRSNT pins of the bus. Once the frequency of the S_CLK input is stable, the clock circuit can assert the

S_CLK_STABLE signal to allow the bridge to complete the reset sequence. The clock generation circuitry

must ensure that the clock frequency it provides falls within the range that the bridge will ultimately determine

and broadcast on the initialization pattern. To do this, the clock generator may need to drive the proper values

on the S_SEL100 and S_PCIXCAP inputs, in addition to controlling the S_CLK_STABLE signal. A mismatch

between the broadcast initialization pattern and the actual operating mode and frequency of the bus is a

violation of the architecture and will cause unpredictable results.

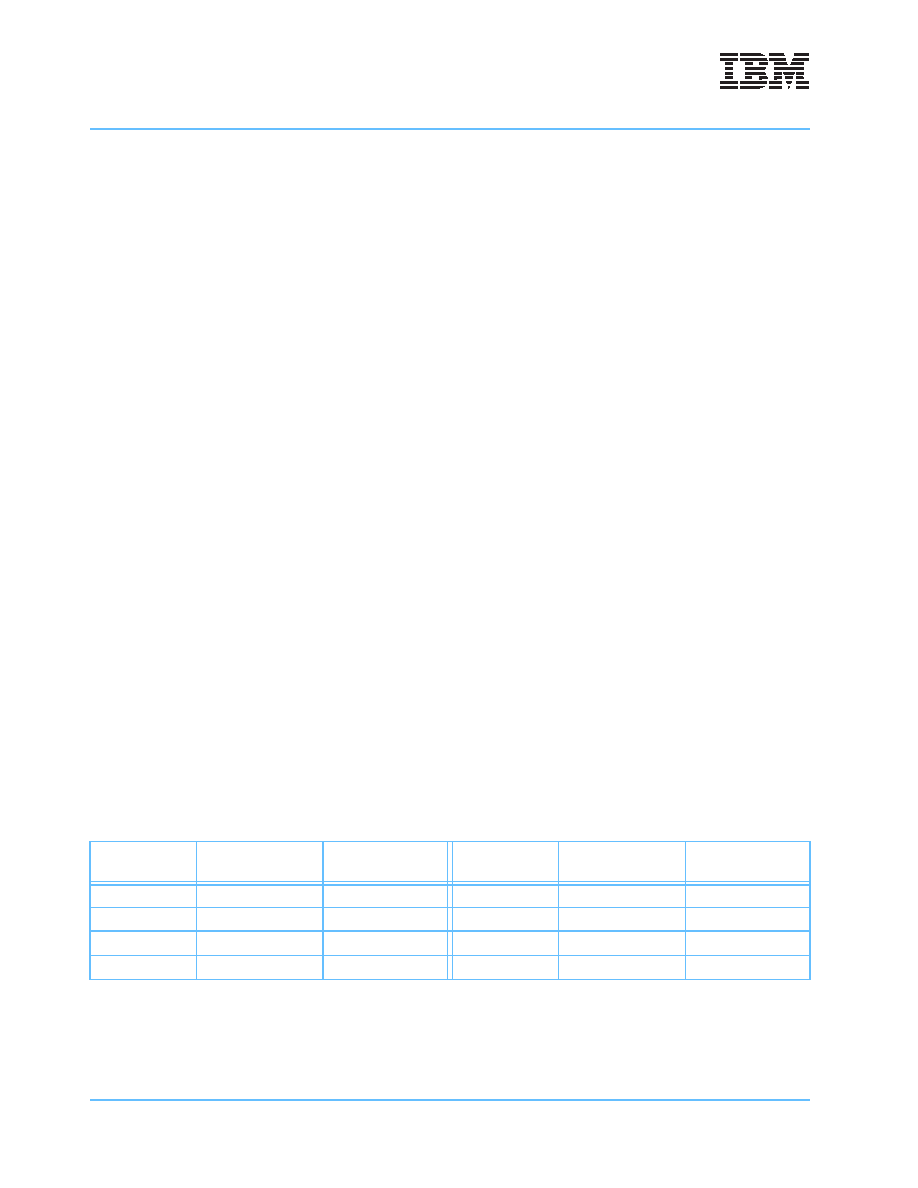

6.5 Driver Impedance Selection

On the IBM 133 PCI-X Bridge R2.0, the output drivers for the bussed PCI/PCI-X interface signals are capable

of two different output impedances, a 40 ohm output impedance for point-to-point applications and a 20 ohm

output impedance for multi-point configurations. The output impedance for the primary and secondary inter-

faces is separately controlled. The bridge selects a default impedance value at the de-assertion of the bus

reset on the basis of the bus mode and frequency initialization pattern which was received on the primary

interface or generated on the secondary interface. It is assumed that if a bus is configured to be in the PCI-X

133 mode, it will be lightly loaded and therefore have a higher impedance. The drivers are put into

point-to-point mode for this case. For all other PCI-X and all PCI configurations, the bridge assumes that the

bus is more heavily loaded and has a lower impedance, so the drivers are set to multi-point mode.

There may be some applications for which these assumptions are inaccurate. For example, a conventional

PCI device may be connected in a point-to-point manner. For exceptions like this, two control input signals

are provided, P_DRVR_MODE for the primary interface and S_DRVR_MODE for the secondary interface.

When these inputs are pulled high, the bridge will change the output impedance of the drivers on their respec-

tive interfaces to the opposite state than was assumed by default, as shown in

Table 6-1. Driver Impedance Selection

Primary Bus Mode

Default Driver Mode

(P_DRVR_MODE=0)

Driver Mode if

P_DRVR_MODE=1

Secondary Bus

Mode

Default Driver Mode

(S_DRVR_MODE=0)

Driver Mode if

S_DRVR_MODE=1

Conventional PCI

Multi-point (20

)

Point-to-point (40

)

Conventional PCI

Multi-point (20

)

Point-to-point (40

)

PCI-X 66

Multi-point (20

)

Point-to-point (40

)

PCI-X 66

Multi-point (20

)

Point-to-point (40

)

PCI-X 100

Multi-point (20

)

Point-to-point (40

)

PCI-X 100

Multi-point (20

)

Point-to-point (40

)

PCI-X 133

Point-to-point (40

)

Multi-point (20

)

PCI-X 133

Point-to-point (40

)

Multi-point (20

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25403GCX-3JC76C2 | RISC PROCESSOR, PQFP16 |

| IBM25405GP-3BA200C2 | RISC PROCESSOR, PBGA456 |

| IBM25EMPPC603EFG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PQFP240 |

| IBM25EMPPC603EBG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

| IBM25EMPPC740LDBC4000 | 32-BIT, 400 MHz, RISC PROCESSOR, CBGA255 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM24L5086 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM25403GCX-3BC80C2 | 制造商:IBM 功能描述:RISC PROCESSOR, 160 Pin Plastic BGA |

| IBM25403GCX-3JC50C2 | 制造商:IBM 功能描述:403GCX-3JC50C2 |

| IBM25403GCX-3JC66C2 | 制造商:IBM 功能描述: |

| IBM25403GCX3JC76C2 | 制造商:IBM 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。