- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385942 > TNETA1560 (Texas Instruments, Inc.) ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機(jī)接口) PDF資料下載

參數(shù)資料

| 型號: | TNETA1560 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機(jī)接口) |

| 中文描述: | 自動柜員機(jī)分段和重組與SBus主機(jī)接口(自動柜員機(jī)分段和重設(shè)裝置帶SBU的主機(jī)接口設(shè)備) |

| 文件頁數(shù): | 14/40頁 |

| 文件大小: | 804K |

| 代理商: | TNETA1560 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

TNETA1560

ATM SEGMENTATION AND REASSEMBLY DEVICE

WITH SBUS HOST INTERFACE

SDNS010C – JANUARY 1994 – REVISED OCTOBER 1995

14

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

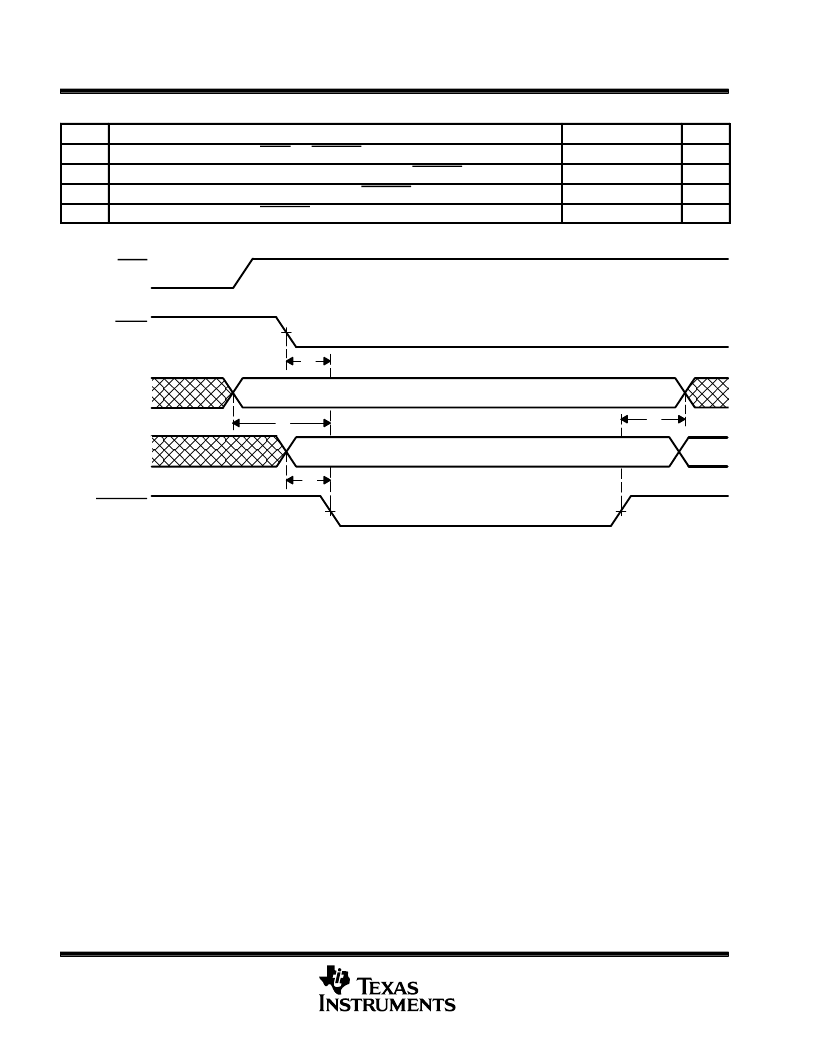

operating characteristics (see Figure 8)

NO.

MIN

TYP

MAX

UNIT

1

td(LBPHYCS)1

td(LBPHYCS)2

td(LBPHYCS)3

td(LBADDR)

Delay time, LBRW

↓

to LBPHYCS

↓

40

ns

2

Delay time, LBADDR15–LBADDR0 valid to LBPHYCS

↓

160

ns

3

Delay time, LBD7–LBD0 valid to LBPHYCS

↓

40

ns

4

Delay time, LBPHYCS

↑

to LBADDR15–LBADDR0 invalid

126

ns

The typical values are given for operation with a 25-MHz SBus clock.

LBRW

(output)

LBRD

(output)

LBADDR15–

LBADDR0

(output)

LBD7–

LBD0

(output)

LBPHYCS

(output)

2

3

4

1

Figure 8. Local-Bus-Interface Write Operation (TNETA1560 as Slave)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TNETA1561 | ATM Segmentation and Reassembly Device with PCI Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機(jī)接口) |

| TNETA1600 | SONET/SDH ATM Receiver/Transmitter for 622.08-Mit/s or 155.52-Mbit/s Operation(SONET/SDH ATM接收器/傳送器) |

| TNETA1610 | STS-12c/STM-4 Receiver/Transmitter with Clock Recovery/Generation(STS-12C/STM-4接收/傳送器) |

| TNETA1611 | STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) |

| TNETA1630 | 622.08-MHz Clock-Recovery Device(622.08-MHz時鐘發(fā)生裝置) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1560MFP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TNETA1560PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1561PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1570 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE |

| TNETA1570MFP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Segmentation and Reassembly Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。