- 您現(xiàn)在的位置:買賣IC網 > PDF目錄385942 > TNETA1560 (Texas Instruments, Inc.) ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設裝置帶SBUS主機接口) PDF資料下載

參數(shù)資料

| 型號: | TNETA1560 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設裝置帶SBUS主機接口) |

| 中文描述: | 自動柜員機分段和重組與SBus主機接口(自動柜員機分段和重設裝置帶SBU的主機接口設備) |

| 文件頁數(shù): | 5/40頁 |

| 文件大小: | 804K |

| 代理商: | TNETA1560 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

TNETA1560

ATM SEGMENTATION AND REASSEMBLY DEVICE

WITH SBUS HOST INTERFACE

SDNS010C – JANUARY 1994 – REVISED OCTOBER 1995

5

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

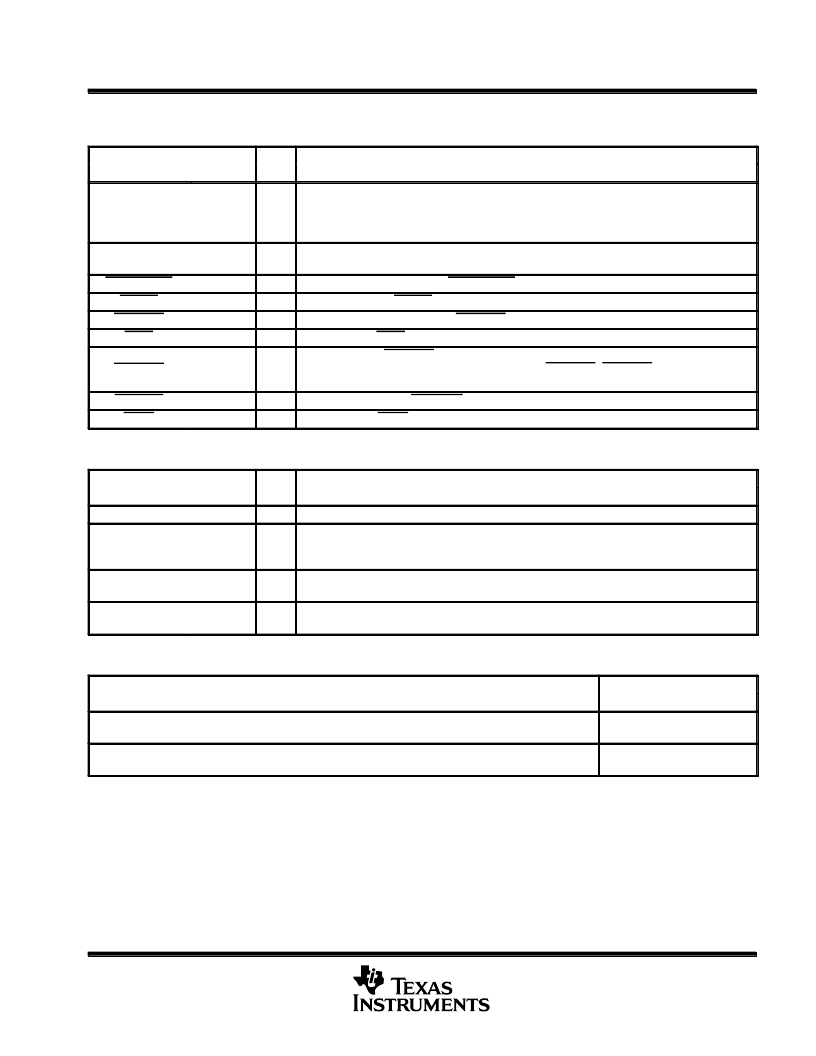

Terminal Functions (Continued)

local-bus interface

TERMINAL

NAME

I/O

DESCRIPTION

NO.

LBADDR15–

LBADDR0

181–183,

185–189,

192–195,

197–200

O

Local-bus address. LBADDR15–LBADDR0 are the lower 16 bits of the SBus address bus and are

routed directly to the local-bus-address lines.

LBD7 – LBD0

161–165,

167–169

I/O

Local-bus data. LBD7–LBD0 are used to transfer data to/from local slave devices.

LBEPROMCS

170

O

Local-bus EPROM chip-select. LBEPROMCS is an active-low signal.

LBINTR

179

I

Local-bus interrupt. LBINTR is generated by a local-bus device.

LBPHYCS

171

O

Local-bus PHY-layer chip select. LBPHYCS is used to select PHY-layer devices.

LBRD

174

O

Local-bus read. LBRD is an active-low signal that indicates a read operation.

LBREADY

180

I

Local-bus-ready. LBREADY is driven by local slave devices. The bus transaction must be

completed after eight SBus cycles regardless of LBREADY. LBREADY is accepted by the

TNETA1560 as a handshake from the devices on the bus.

LBRESET

175

O

Local-bus reset output. LBRESET is an active-low signal.

LBRW

173

O

Local-bus write. LBRW is an active-low signal that indicates a write operation.

control and configuration

TERMINAL

NAME

I/O

DESCRIPTION

NO.

PHYCLOCK

177

I

PHY-layer clock. PHYCLOCK is a 19.44-MHz clock signal driven by a PHY-layer clock crystal.

TESTI3–TESTI0

147,

149,

233–234

I/O

Test signals. TEST13–TESTI0 are for manufacturer use only. These signals are tied low for normal

operation.

TESTMODE

151

I

Test-mode configuration. TESTMODE is tied low for normal operation. TESTMODE is for

manufacturer use only.

TESTO7–TESTO0

152–159

I/O

Test signals. TESTO7–TESTO0 are left open for normal operation. TESTO7–TESTO0 are for

manufacturer use only.

power and ground

TERMINAL

DESCRIPTION

NAME

NO.

GND

4, 16, 23, 28, 40, 47, 52, 56, 64, 71, 76, 83, 88, 95, 100, 107, 112, 117, 124, 136, 148, 160,

172, 176, 184, 191, 196, 208, 220, 232, 235, 237

Ground

VCC

10, 22, 34, 41, 46, 58, 65, 70, 77, 82, 89, 94, 101, 106, 113, 118, 130, 137, 142, 166, 178,

190, 202, 214, 226, 238

Supply voltage

相關PDF資料 |

PDF描述 |

|---|---|

| TNETA1561 | ATM Segmentation and Reassembly Device with PCI Host Interface(ATM 分段和重設裝置帶SBUS主機接口) |

| TNETA1600 | SONET/SDH ATM Receiver/Transmitter for 622.08-Mit/s or 155.52-Mbit/s Operation(SONET/SDH ATM接收器/傳送器) |

| TNETA1610 | STS-12c/STM-4 Receiver/Transmitter with Clock Recovery/Generation(STS-12C/STM-4接收/傳送器) |

| TNETA1611 | STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) |

| TNETA1630 | 622.08-MHz Clock-Recovery Device(622.08-MHz時鐘發(fā)生裝置) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1560MFP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TNETA1560PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1561PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1570 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE |

| TNETA1570MFP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Segmentation and Reassembly Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復。