- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385942 > TNETA1560 (Texas Instruments, Inc.) ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設裝置帶SBUS主機接口) PDF資料下載

參數(shù)資料

| 型號: | TNETA1560 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設裝置帶SBUS主機接口) |

| 中文描述: | 自動柜員機分段和重組與SBus主機接口(自動柜員機分段和重設裝置帶SBU的主機接口設備) |

| 文件頁數(shù): | 4/40頁 |

| 文件大?。?/td> | 804K |

| 代理商: | TNETA1560 |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

TNETA1560

ATM SEGMENTATION AND REASSEMBLY DEVICE

WITH SBUS HOST INTERFACE

SDNS010C – JANUARY 1994 – REVISED OCTOBER 1995

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

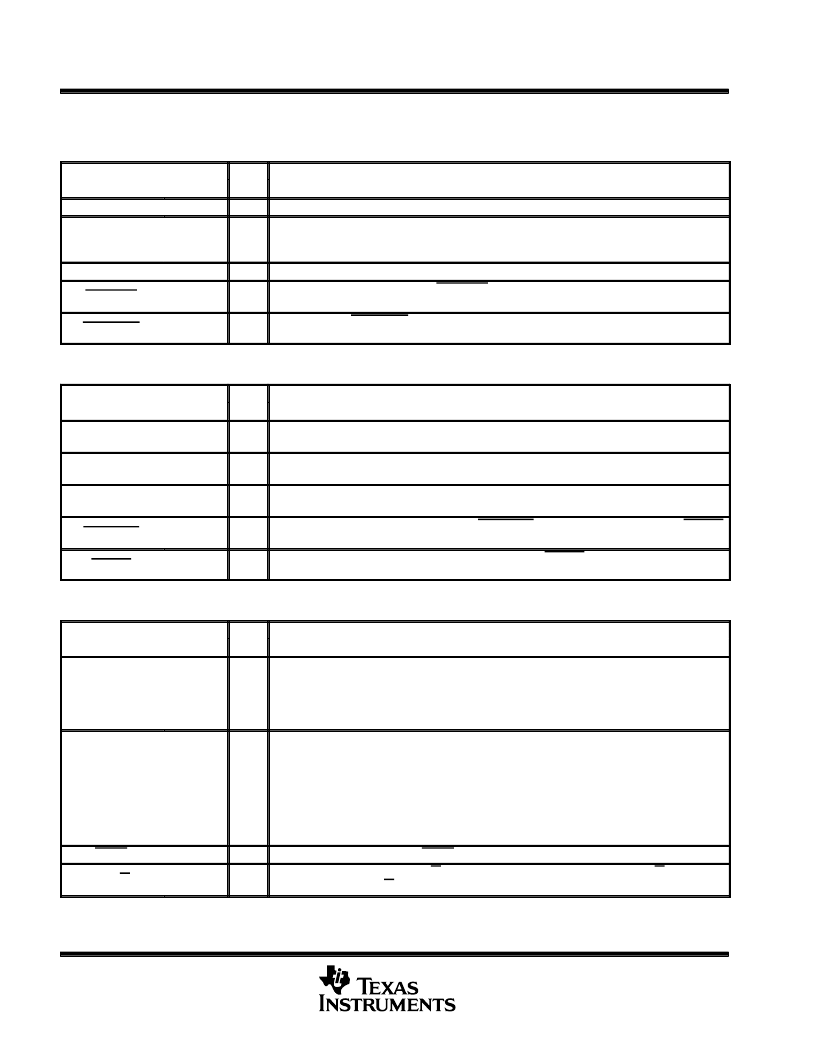

Terminal Functions (Continued)

PHY-layer receive interface

TERMINAL

NAME

I/O

DESCRIPTION

NO.

RCLK

215

O

Receive clock. RCLK is equivalent to the internal clock at 19.44 MHz. RCLK is sent to the PHY layer.

RDATA7–RDATA0

201.

203–207,

209–210

I

Receive data. RDATA7–RDATA0 are connected to the PHY-layer receive interface.

RSOC

213

I

Receive start of cell. The PHY layer sends RSOC with the output data.

RXEMPTY

212

I

Receive buffer empty in PHY layer. RXEMPTY acts as an inverted enable signal on the PHY-layer

receive.

RXENABLE

211

O

Receive enable. RXENABLE is always high. For proper operation with a PHY-layer device, leave

it open or invert it before going to the PHY layer.

PHY-layer transmit interface

TERMINAL

NAME

I/O

DESCRIPTION

NO.

TCLK

229

O

Transmit clock. The TNETA1560 generates TCLK at the SBus frequency and sends it to the PHY

layer.

TDATA7–TDATA0

217–219,

221–225

O

Transmit data. TDATA7–TDATA0 are sent at the rate of the SBus clock and are driven by the

TNETA1560.

TSOC

227

O

Transmit start of cell. TSOC is sent to the PHY layer with the transmit output data and indicates that

the first byte of an ATM cell was transmitted to the PHY layer.

TXENABLE

228

O

Transmit enable. The TNETA1560 turns off TXENABLE when the PHY layer sends the TXFULL

signal.

TXFULL

216

I

Transmit buffer full in the PHY layer. The PHY layer asserts TXFULL at least four cycles before any

internal buffers are full. This makes the TNETA1560 stop the data transmission to the PHY layer.

control-memory interface

TERMINAL

NAME

I/O

DESCRIPTION

NO.

CMADDR13–

CMADDR0

236

239–240,

1–3,

5–9,

11–13

14–15

17–21,

24–27,

29–33,

35–39,

42–45,

48–51,

53–55

O

Control-memory address. CMADDR13–CMADDR0 are used to access the data structures in

control memory.

CMD31–CMD0

I/O

Control-memory data bus. CMD31–CMD0 is a 32-bit data bus. This control-memory interface is

designed for 20-ns asynchronous SRAMs. The TNETA1560 uses CMD31–CMD0 to write and

read data from its data structures in the control memory.

CMOE

230

O

Control-memory output enable. CMOE is an active-low signal.

CMR/W

231

O

Control-memory read/write. CMR/W determines a read or write operation. If CMR/W is low, it is a

write operation. If CMR/W is high, it is a read operation.

相關PDF資料 |

PDF描述 |

|---|---|

| TNETA1561 | ATM Segmentation and Reassembly Device with PCI Host Interface(ATM 分段和重設裝置帶SBUS主機接口) |

| TNETA1600 | SONET/SDH ATM Receiver/Transmitter for 622.08-Mit/s or 155.52-Mbit/s Operation(SONET/SDH ATM接收器/傳送器) |

| TNETA1610 | STS-12c/STM-4 Receiver/Transmitter with Clock Recovery/Generation(STS-12C/STM-4接收/傳送器) |

| TNETA1611 | STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) |

| TNETA1630 | 622.08-MHz Clock-Recovery Device(622.08-MHz時鐘發(fā)生裝置) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1560MFP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TNETA1560PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1561PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1570 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE |

| TNETA1570MFP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Segmentation and Reassembly Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復。