- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385942 > TNETA1560 (Texas Instruments, Inc.) ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設裝置帶SBUS主機接口) PDF資料下載

參數(shù)資料

| 型號: | TNETA1560 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設裝置帶SBUS主機接口) |

| 中文描述: | 自動柜員機分段和重組與SBus主機接口(自動柜員機分段和重設裝置帶SBU的主機接口設備) |

| 文件頁數(shù): | 18/40頁 |

| 文件大?。?/td> | 804K |

| 代理商: | TNETA1560 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

TNETA1560

ATM SEGMENTATION AND REASSEMBLY DEVICE

WITH SBUS HOST INTERFACE

SDNS010C – JANUARY 1994 – REVISED OCTOBER 1995

18

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

bandwidth group (BWG) table mechanism

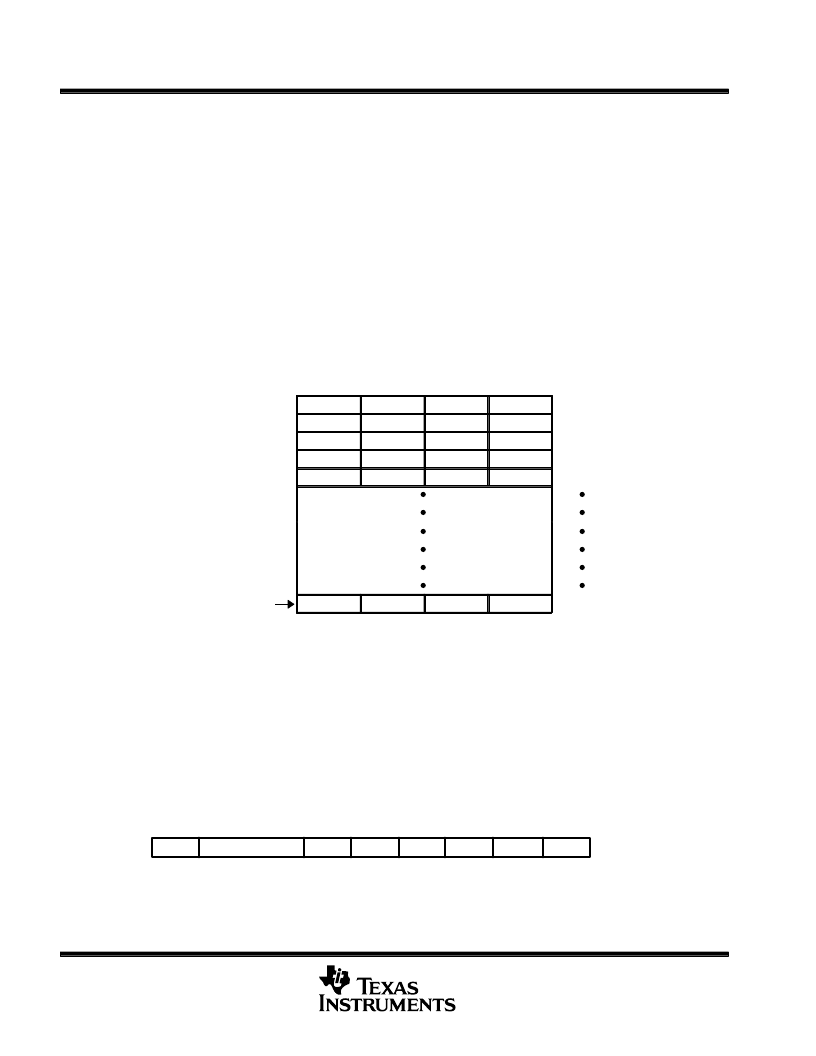

The SAR generates data via a special bit-rate control table known as the BWG table (see Figure 12). The BWG

table consists of up to 4800 entries and each entry consists of an 8-bit BWG index. The table is organized with

1200 words in control memory. The size is programmable via the BWG-size register. Since each BWG index

corresponds to a transmit direct-memory access (DMA) channel, the TNETA1560 can support 255 (8-bit Index)

transmit DMA channels simultaneously. The SAR cycles through the table and sends an ATM cell for the

transmit DMA channel for each entry in the table. If a zero value is entered for a BWG index, an idle cell is

transmitted. The BWG table is used to assign the transmit-side bandwidth. The total available bandwidth for

an OC3c SONET link is 135.63 Mbit/s (155.52 Mbit/s less SONET and ATM overhead). The granularity is

obtained by dividing the SONET-link bit rate (135.63 Mbit/s) by the entries in the BWG table (4800). Thus, an

application requiring 500 kbit/s requires 19 entries in the table.

500 kbit/s/28250 bit/s per entry = 19 required entries in the table.

If the application uses the transmit descriptor ring 5, there will be 19 entries, with 5 as the BWG index in the BWG

table shown in Figure 12.

5

5

5

5

0

5

5

5

5

1

5

5

5

5

2

5

5

5

5

3

5

5

5

0

4

Send Idle Cell if 0

0

0

0

0

1199

Figure 12. BWG Table

AAL-type processing

The SBus SAR supports various types of AAL processing. AAL3/4, AAL5, null-AAL, GFC, and OAM processing

are described in this section.

AAL3/4 processing

Since 48 bytes are provided across the SBus interface, all AAL3/4 packet data processing is performed by the

host in software. AAL5 processing is disabled on VCIs using AAL3/4. The AAL3/4 EOM indicator, which is

located in the first byte of the ATM payload (see Figure 13), is recognized in hardware, initiating an interrupt to

the host.

Bit 7

Bit 0

AAL3/4 EOM Bit

Figure 13. AAL3/4 Processing

相關PDF資料 |

PDF描述 |

|---|---|

| TNETA1561 | ATM Segmentation and Reassembly Device with PCI Host Interface(ATM 分段和重設裝置帶SBUS主機接口) |

| TNETA1600 | SONET/SDH ATM Receiver/Transmitter for 622.08-Mit/s or 155.52-Mbit/s Operation(SONET/SDH ATM接收器/傳送器) |

| TNETA1610 | STS-12c/STM-4 Receiver/Transmitter with Clock Recovery/Generation(STS-12C/STM-4接收/傳送器) |

| TNETA1611 | STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) |

| TNETA1630 | 622.08-MHz Clock-Recovery Device(622.08-MHz時鐘發(fā)生裝置) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1560MFP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TNETA1560PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1561PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1570 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE |

| TNETA1570MFP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Segmentation and Reassembly Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復。