- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385942 > TNETA1560 (Texas Instruments, Inc.) ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機接口) PDF資料下載

參數(shù)資料

| 型號: | TNETA1560 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機接口) |

| 中文描述: | 自動柜員機分段和重組與SBus主機接口(自動柜員機分段和重設(shè)裝置帶SBU的主機接口設(shè)備) |

| 文件頁數(shù): | 2/40頁 |

| 文件大?。?/td> | 804K |

| 代理商: | TNETA1560 |

第1頁當前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

TNETA1560

ATM SEGMENTATION AND REASSEMBLY DEVICE

WITH SBUS HOST INTERFACE

SDNS010C – JANUARY 1994 – REVISED OCTOBER 1995

2

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

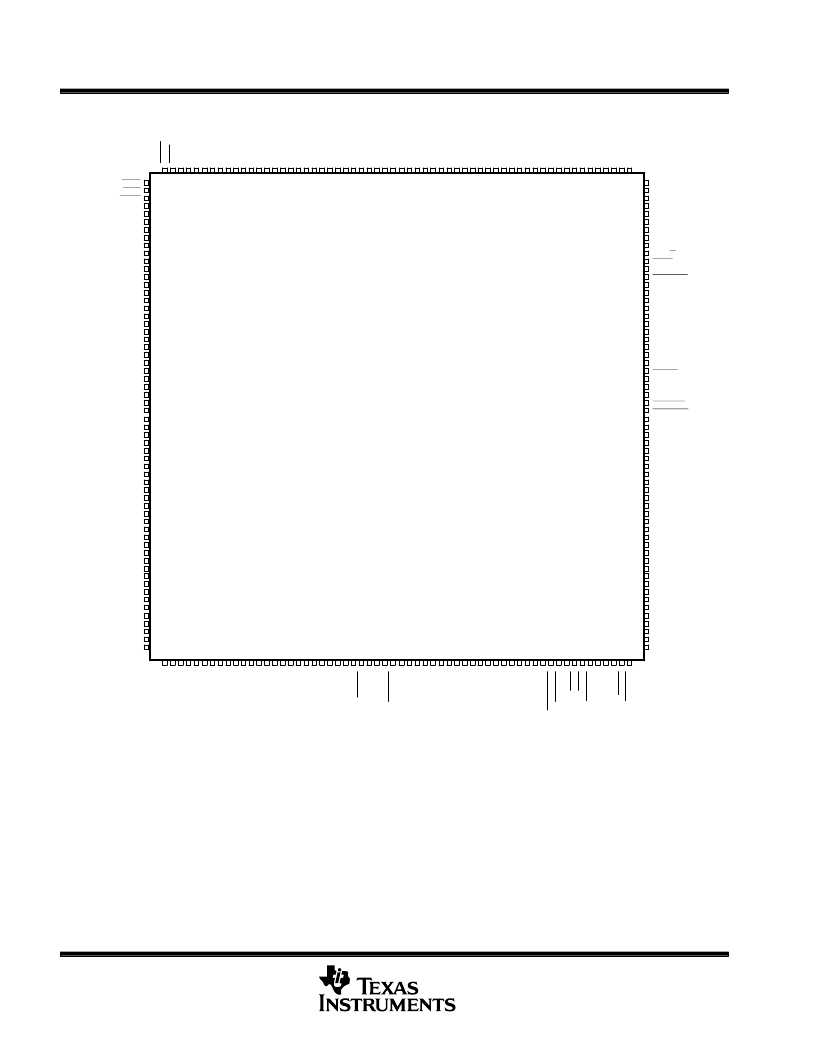

PGC PACKAGE

(TOP VIEW)

SBBG

SBAS

SBIRQ

GND

V

CC

SBD0

SBD1

SBD2

SBD3

V

CC

GND

SBD4

SBD5

SBD6

SBD7

GND

V

CC

SBD8

SBD9

SBD10

SBD11

V

CC

GND

SBD12

SBD13

SBD14

SBD15

GND

V

CC

SBD16

SBD17

SBD18

SBD19

V

CC

GND

SBD20

SBD21

SBD22

SBD23

GND

V

CC

SBD24

SBD25

SBD26

SBD27

V

CC

GND

SBD28

SBD29

SBD30

SBD31

GND

V

CC

SBPA0

SBPA1

SBPA2

GND

V

CC

SBPA3

SBPA4

CMADDR2

CMADDR1

V

GND

CMADDR0

GND

TESTI3

TESTI2

GND

CMR/W

CMOE

TCLK

TXENABLE

TSOC

V

TDATA7

TDATA6

TDATA5

TDATA4

TDATA3

GND

TDATA2

TDATA1

TDATA0

TXFULL

RCLK

V

RSOC

RXEMPTY

RXENABLE

RDATA7

RDATA6

GND

RDATA5

RDATA4

RDATA3

RDATA2

RDATA1

V

RDATA0

LBADDR15

LBADDR14

LBADDR13

LBADDR12

GND

LBADDR11

LBADDR10

LBADDR9

LBADDR8

GND

V

LBADDR7

LBADDR6

LBADDR5

LBADDR4

LBADDR3

GND

LBADDR2

LBADDR1

LBADDR0

S

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

239

237

235

233

231

229

227

225

223

221

219

217

215

213

211

209

207

205

203

201

199

197

195

193

191

189

187

185

183

181

S

V

S

G

C

C

C

G

C

C

C

C

G

C

C

C

C

G

C

C

C

C

C

C

C

C

C

C

G

C

C

C

C

G

C

C

C

C

C

G

C

C

C

C

C

C

C

C

C

G

C

C

C

S

G

S

S

S

S

S

C

S

S

S

S

S

G

S

S

S

S

S

S

S

S

T

G

T

S

T

T

T

T

T

T

T

T

T

G

L

L

L

L

L

L

L

L

L

L

G

L

L

L

G

P

L

L

S

S

C

V

C

V

C

V

C

V

C

V

C

C

V

C

V

C

V

C

V

C

V

5

5

5

5

5

4

4

4

4

4

3

3

3

3

3

2

2

2

2

2

1

1

1

1

1

9

7

5

3

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

description (continued)

The native clock for the TNETA1560 is the SBus clock, which can range between 16.67 MHz and 25 MHz. The

native-word size for the device is 32 bits, corresponding to the data width for the SBus. The control-memory

interface is 32 bits wide. This interface allows the device to access the local memory to obtain the control

information on the packets being segmented and reassembled and to obtain their locations in host memory.

Each packet queued for transmission can be distributed across multiple buffers in host memory with each

starting at any byte boundary. This is supported in hardware by the device. Every received package is placed

in a single buffer in the host memory and is aligned to a 16-byte boundary. The TNETA1560 operation is

explained in detail in the Principles of Operation section.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TNETA1561 | ATM Segmentation and Reassembly Device with PCI Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機接口) |

| TNETA1600 | SONET/SDH ATM Receiver/Transmitter for 622.08-Mit/s or 155.52-Mbit/s Operation(SONET/SDH ATM接收器/傳送器) |

| TNETA1610 | STS-12c/STM-4 Receiver/Transmitter with Clock Recovery/Generation(STS-12C/STM-4接收/傳送器) |

| TNETA1611 | STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) |

| TNETA1630 | 622.08-MHz Clock-Recovery Device(622.08-MHz時鐘發(fā)生裝置) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1560MFP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TNETA1560PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1561PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1570 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE |

| TNETA1570MFP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Segmentation and Reassembly Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。