- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4287 > XC3S400AN-5FTG256C (Xilinx Inc)IC FPGA SPARTAN-3AN 256FTBGA PDF資料下載

參數(shù)資料

| 型號: | XC3S400AN-5FTG256C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 24/123頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3AN 256FTBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 896 |

| 邏輯元件/單元數(shù): | 8064 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 195 |

| 門數(shù): | 400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁

DS557 (v4.1) April 1, 2011

Product Specification

12

Copyright 2007–2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and

other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

DC Electrical Characteristics

In this section, specifications can be designated as

Advance, Preliminary, or Production. These terms are

defined as follows:

Advance: Initial estimates are based on simulation, early

characterization, and/or extrapolation from the

characteristics of other families. Values are subject to

change. Use as estimates, not for production.

Preliminary: Based on characterization. Further changes

are not expected.

Production: These specifications are approved once the

silicon has been characterized over numerous production

lots. Parameter values are considered stable with no future

changes expected.

All parameter limits are representative of worst-case supply

voltage and junction temperature conditions. Unless

otherwise noted, the published parameter values apply

to all Spartan-3AN devices. AC and DC characteristics

are specified using the same numbers for both

commercial and industrial grades.

Absolute Maximum Ratings

Maximum Ratings might cause permanent damage to the

device. These are stress ratings only; functional operation

of the device at these or any other conditions beyond those

listed under the Recommended Operating Conditions is not

implied. Exposure to absolute maximum conditions for

extended periods of time adversely affects device reliability.

70

Spartan-3AN FPGA Family:

DC and Switching Characteristics

DS557 (v4.1) April 1, 2011

Product Specification

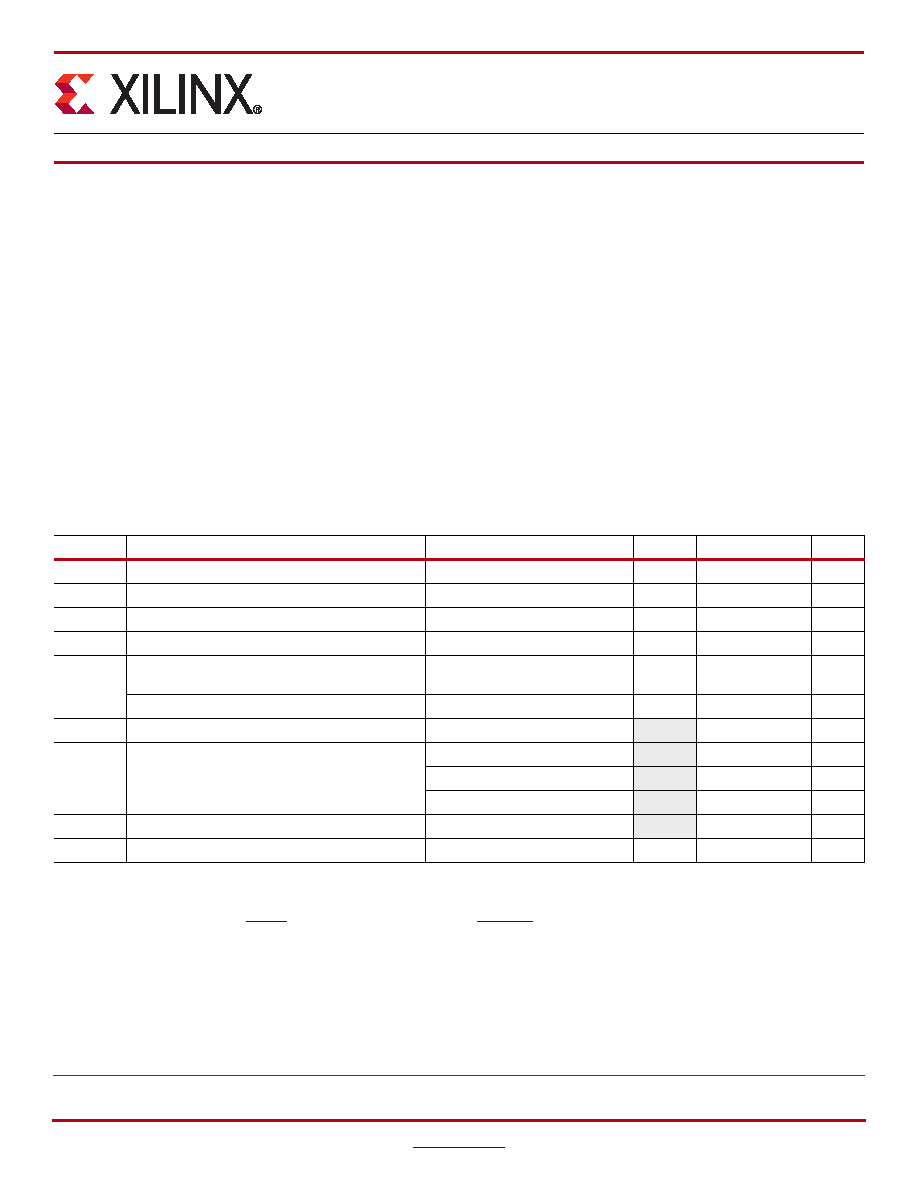

Table 6: Absolute Maximum Ratings

Symbol

Description

Conditions

Min

Max

Units

VCCINT

Internal supply voltage

–0.5

1.32

V

VCCAUX

Auxiliary supply voltage

–0.5

3.75

V

VCCO

Output driver supply voltage

–0.5

3.75

V

VREF

Input reference voltage

–0.5

VCCO +0.5

V

VIN

Voltage applied to all User I/O pins and

dual-purpose pins

Driver in a high-impedance state

–0.95

4.6

V

Voltage applied to all Dedicated pins

–0.5

4.6

V

IIK

Input clamp current per I/O pin

–

±100

mA

VESD

Electrostatic Discharge Voltage

Human body model

–

±2000

V

Charged device model

–

±500

V

Machine model

–

±200

V

TJ

Junction temperature

–125

°C

TSTG

Storage temperature

–65

150

°C

Notes:

1.

Upper clamp applies only when using PCI IOSTANDARDs.

1.

For soldering guidelines, see UG112: Device Package User Guide and XAPP427: Implementation and Solder Reflow Guidelines for Pb-Free

Packages.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC024T-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XA2S100E-6TQ144I | IC FPGA SPARTAN-IIE 144TQFP |

| 24LC024-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| 24LC025-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XC6SLX9-L1FT256I | IC FPGA SPARTAN 6 256FTGBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S5000-4FG1156C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156CES | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156I | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG676C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

| XC3S5000-4FG676I | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。