- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4287 > XC3S400AN-5FTG256C (Xilinx Inc)IC FPGA SPARTAN-3AN 256FTBGA PDF資料下載

參數(shù)資料

| 型號: | XC3S400AN-5FTG256C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 43/123頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3AN 256FTBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 896 |

| 邏輯元件/單元數(shù): | 8064 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 195 |

| 門數(shù): | 400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁

Spartan-3AN FPGA Family: DC and Switching Characteristics

DS557 (v4.1) April 1, 2011

Product Specification

26

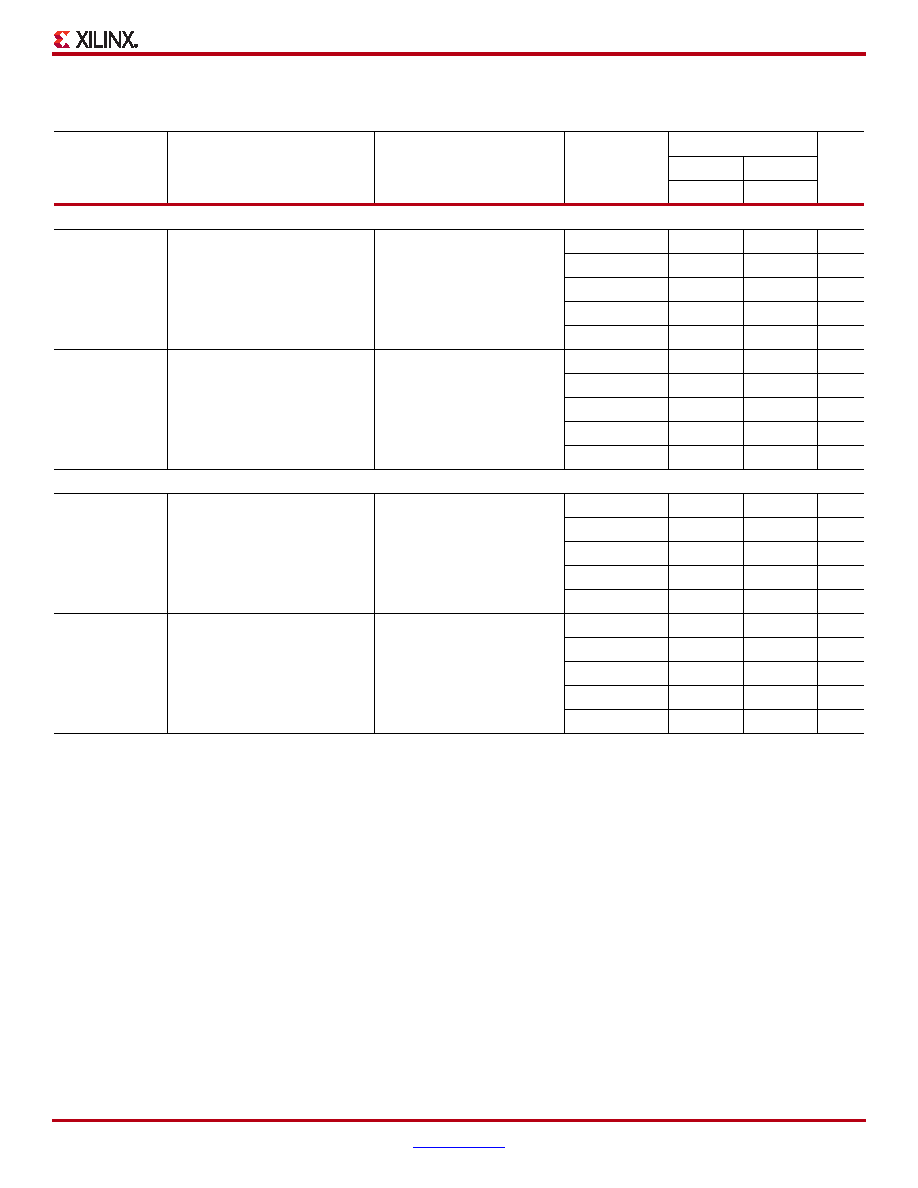

Pin-to-Pin Setup and Hold Times

Table 22: Pin-to-Pin Setup and Hold Times for the IOB Input Path (System Synchronous)

Symbol

Description

Conditions

Device

Speed Grade

Units

-5

-4

Min

Setup Times

TPSDCM

When writing to the Input

Flip-Flop (IFF), the time from the

setup of data at the Input pin to

the active transition at a Global

Clock pin. The DCM is in use. No

Input Delay is programmed.

LVCMOS25(2),

IFD_DELAY_VALUE = 0,

with DCM(4)

XC3S50AN

2.45

2.68

ns

XC3S200AN

2.59

2.84

ns

XC3S400AN

2.38

2.68

ns

XC3S700AN

2.38

2.57

ns

XC3S1400AN

1.91

2.17

ns

TPSFD

When writing to IFF, the time from

the setup of data at the Input pin

to an active transition at the

Global Clock pin. The DCM is not

in use. The Input Delay is

programmed.

LVCMOS25(2),

IFD_DELAY_VALUE = 5,

without DCM

XC3S50AN

2.55

2.76

ns

XC3S200AN

2.32

2.76

ns

XC3S400AN

2.21

2.60

ns

XC3S700AN

2.28

2.63

ns

XC3S1400AN

2.33

2.41

ns

Hold Times

TPHDCM

When writing to IFF, the time from

the active transition at the Global

Clock pin to the point when data

must be held at the Input pin. The

DCM is in use. No Input Delay is

programmed.

LVCMOS25(3),

IFD_DELAY_VALUE = 0,

with DCM(4)

XC3S50AN

–0.36

ns

XC3S200AN

–0.52

ns

XC3S400AN

–0.33

–0.29

ns

XC3S700AN

–0.17

–0.12

ns

XC3S1400AN

–0.07

0.00

ns

TPHFD

When writing to IFF, the time from

the active transition at the Global

Clock pin to the point when data

must be held at the Input pin. The

DCM is not in use. The Input

Delay is programmed.

LVCMOS25(3),

IFD_DELAY_VALUE = 5,

without DCM

XC3S50AN

–0.63

–0.58

ns

XC3S200AN

–0.56

ns

XC3S400AN

–0.42

ns

XC3S700AN

–0.80

–0.75

ns

XC3S1400AN

–0.69

ns

Notes:

1.

The numbers in this table are tested using the methodology presented in Table 30 and are based on the operating conditions set forth in

2.

This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data

Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 26. If this is true of the data Input, add the

appropriate Input adjustment from the same table.

3.

This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data

Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Table 26. If this is true of the data Input, subtract the

appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock’s active

edge.

4.

DCM output jitter is included in all measurements.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC024T-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XA2S100E-6TQ144I | IC FPGA SPARTAN-IIE 144TQFP |

| 24LC024-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| 24LC025-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XC6SLX9-L1FT256I | IC FPGA SPARTAN 6 256FTGBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S5000-4FG1156C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156CES | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156I | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG676C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

| XC3S5000-4FG676I | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。