- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4287 > XC3S400AN-5FTG256C (Xilinx Inc)IC FPGA SPARTAN-3AN 256FTBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC3S400AN-5FTG256C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 58/123頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3AN 256FTBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 896 |

| 邏輯元件/單元數(shù): | 8064 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 195 |

| 門(mén)數(shù): | 400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)當(dāng)前第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

Spartan-3AN FPGA Family: Introduction and Ordering Information

DS557 (v4.1) April 1, 2011

Product Specification

4

Configuration

Spartan-3AN FPGAs are programmed by loading

configuration data into robust, reprogrammable, static

CMOS configuration latches (CCLs) that collectively control

all functional elements and routing resources. The FPGA’s

configuration data is stored on-chip in nonvolatile Flash

memory, or externally in a PROM or some other nonvolatile

medium, either on or off the board. After applying power, the

configuration data is written to the FPGA using any of seven

different modes:

Configure from internal SPI Flash memory (Figure 2)

Completely self-contained

Reduced board space

Easy-to-use configuration interface

Master Serial from a Xilinx Platform Flash PROM

Serial Peripheral Interface (SPI) from an external

industry-standard SPI serial Flash

Byte Peripheral Interface (BPI) Up from an

industry-standard x8 or x8/x16 parallel NOR Flash

Slave Serial, typically downloaded from a processor

Slave Parallel, typically downloaded from a processor

Boundary-Scan (JTAG), typically downloaded from a

processor or system tester

The MultiBoot feature stores multiple configuration files in

the on-chip Flash, providing extended life with field

upgrades. MultiBoot also supports multiple system

solutions with a single board to minimize inventory and

simplify the addition of new features, even in the field.

Flexibility is maintained to do additional MultiBoot

configurations via the external configuration method.

The Spartan-3AN device authentication protocol prevents

cloning. Design cloning, unauthorized overbuilding, and

complete reverse engineering have driven device security

requirements to higher and higher levels. Authentication

moves the security from bitstream protection to the next

generation of design-level security protecting both the

design and embedded microcode. The authentication

algorithm is entirely user defined, implemented using FPGA

logic. Every product, generation, or design can have a

different algorithm and functionality to enhance security.

In-System Flash Memory

Each Spartan-3AN FPGA contains abundant integrated SPI

serial Flash memory, shown in Table 3, used primarily to

store the FPGA’s configuration bitstream. However, the

Flash memory array is large enough to store at least two

MultiBoot FPGA configuration bitstreams or nonvolatile

data required by the FPGA application, such as

code-shadowed MicroBlaze processor applications.

After configuration, the FPGA design has full access to the

in-system Flash memory via an internal SPI interface; the

control logic is implemented with FPGA logic. Additionally,

the FPGA application itself can store nonvolatile data or

provide live, in-system Flash updates.

The Spartan-3AN device in-system Flash memory supports

leading-edge serial Flash features.

Small page size (264 or 528 bytes) simplifies

nonvolatile data storage

Randomly accessible, byte addressable

Up to 66 MHz serial data transfers

SRAM page buffers

Read Flash data while programming another Flash

page

EEPROM-like byte write functionality

Two buffers in most devices, one in XC3S50AN

Page, Block, and Sector Erase

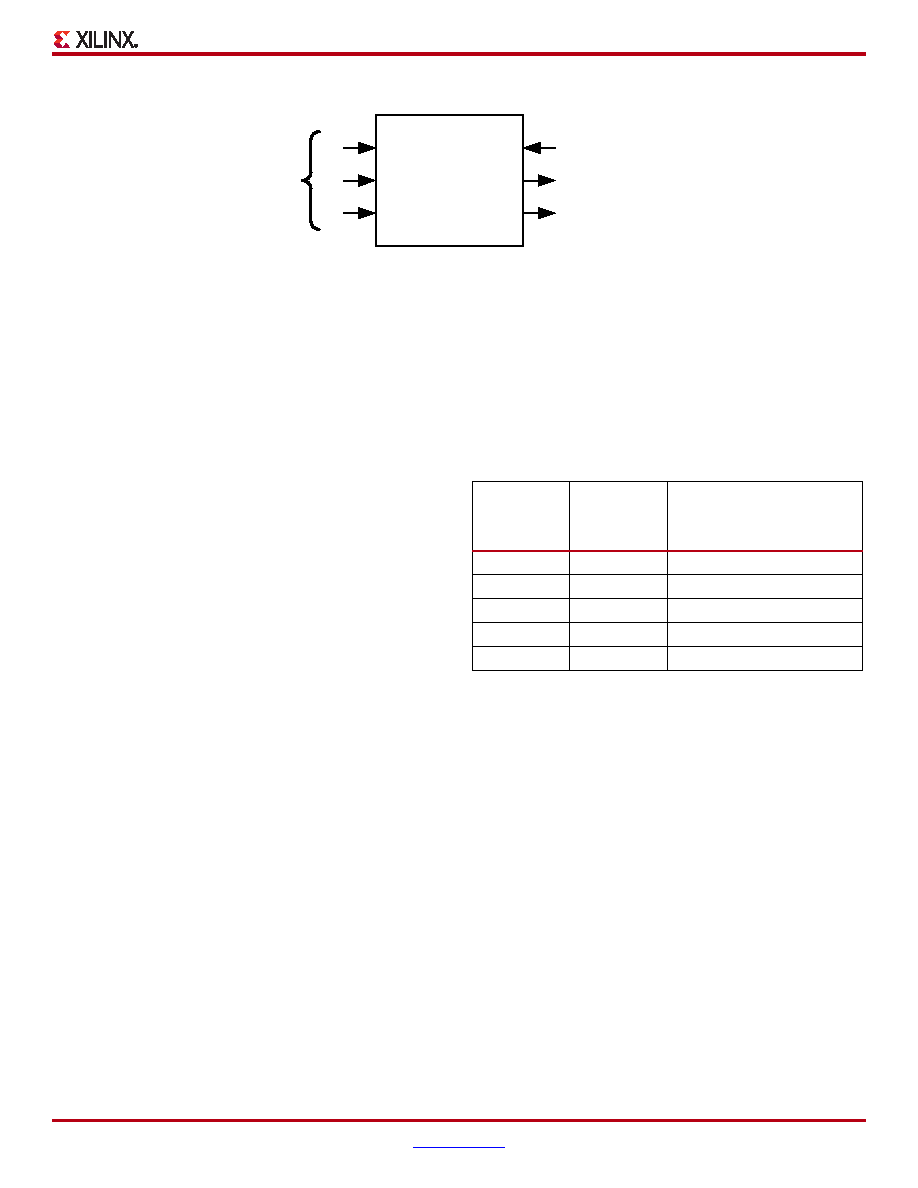

X-Ref Target - Figure 2

Figure 2: Spartan-3AN FPGA Configuration Interface from Internal SPI Flash Memory

M2

M1

M0

VCCAUX

INIT_B

DONE

Spartan-3AN FPGA

‘0’

‘1’

3.3V

Configure

from internal

flash memory

Indicates when

configuration is

finished

DS557-1_06_082810

Table 3: Spartan-3AN Device In-System Flash Memory

Part Number

Total Flash

Memory

(Bits)

FPGA

Bitstream

(Bits)

Additional

Flash

Memory

(Bits)(1)

XC3S50AN

1,081,344

437,312

642,048

XC3S200AN

4,325,376

1,196,128

3,127,872

XC3S400AN

4,325,376

1,886,560

2,437,248

XC3S700AN

8,650,752

2,732,640

5,917,824

XC3S1400AN

17,301,504

4,755,296

12,545,280

Notes:

1.

Aligned to next available page location.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC024T-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XA2S100E-6TQ144I | IC FPGA SPARTAN-IIE 144TQFP |

| 24LC024-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| 24LC025-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XC6SLX9-L1FT256I | IC FPGA SPARTAN 6 256FTGBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S5000-4FG1156C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156CES | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156I | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG676C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

| XC3S5000-4FG676I | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。