- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4287 > XC3S400AN-5FTG256C (Xilinx Inc)IC FPGA SPARTAN-3AN 256FTBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC3S400AN-5FTG256C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 95/123頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3AN 256FTBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 896 |

| 邏輯元件/單元數(shù): | 8064 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 195 |

| 門數(shù): | 400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁當(dāng)前第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁

Spartan-3AN FPGA Family: Pinout Descriptions

DS557 (v4.1) April 1, 2011

Product Specification

73

Electronic versions of the package pinout tables and foot-prints are available for download from the Xilinx website at:

Using a spreadsheet program, the data can be sorted and reformatted according to any specific needs. Similarly, the

ASCII-text file is easily parsed by most scripting programs.

Package Overview

Table 65 shows the five low-cost, space-saving production package styles for the Spartan-3AN family.

Each package style is available in an environmentally friendly lead-free (Pb-free) option. The Pb-free packages include an

extra “G” in the package style name. For example, the standard “CS484” package becomes “CSG484” when ordered as the

Pb-free option. Leaded (Pb) packages are available for selected devices, with the same pinout and without the “G” in the

ordering code; See Table 5, page 7 for more information. The mechanical dimensions of the Pb and Pb-free packages are

similar, as shown in the mechanical drawings provided in Table 66.

For additional package information, see UG112: Device Package User Guide.

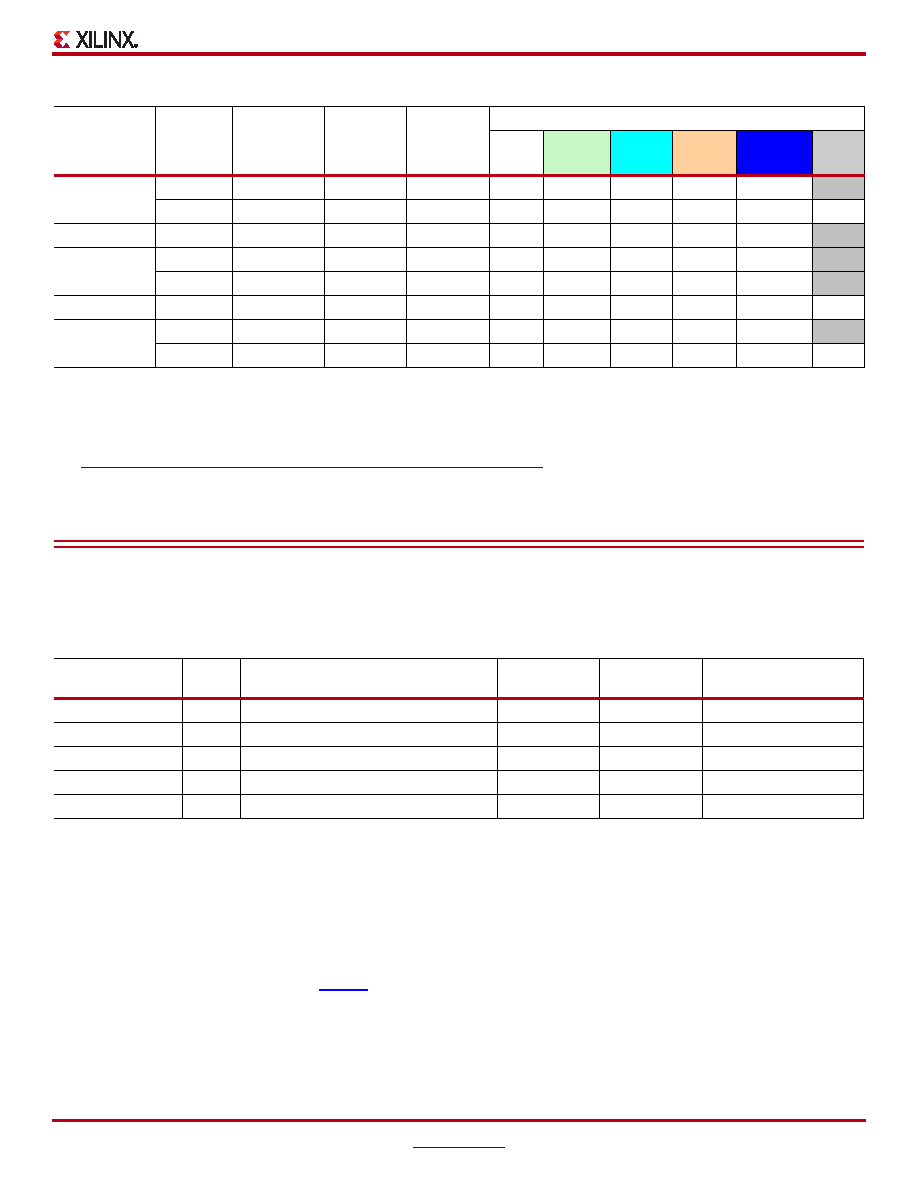

Table 64: Maximum User I/O by Package

Device

Package

Maximum

User I/Os

and

Input-Only

Maximum

Input-

Only

Maximum

Differential

Pairs

All Possible I/Os by Type

I/O

INPUT

DUAL

VREF (1)

CLK

N.C.

XC3S50AN

TQG144

108

7

50

42

2

26

8

30

0

FTG256

144

32

64

53

20

26

15

30

51

XC3S200AN

FTG256

195

35

90

69

21

52

21

32

0

XC3S400AN

FTG256

195

35

90

69

21

52

21

32

0

FGG400

311

63

142

155

46

52

26

32

0

XC3S700AN

FGG484

372

84

165

194

61

52

33

32

3

XC3S1400AN

FGG484

375

87

165

195

62

52

34

32

0

FGG676

502

94

227

313

67

52

38

32

17

Notes:

1.

Some VREFs are on INPUT pins. See pinout tables for details.

Table 65: Spartan-3AN Family Package Options

Package

Leads

Type

Maximum I/Os

Lead Pitch

(mm)

Body Area

(mm)

Height

(mm)

TQ144/TQG144

144

Thin Quad Flat Pack (TQFP)

108

0.5

20 x 20

1.60

FT256/FTG256

256

Fine-pitch Thin Ball Grid Array (FBGA)

195

1.0

17 x 17

1.55

FG400/FGG400

400

Fine-pitch Ball Grid Array (FBGA)

311

1.0

21 x 21

2.43

FG484/FGG484

484

Fine-pitch Ball Grid Array (FBGA)

375

1.0

23 x 23

2.60

FG676/FGG676

676

Fine-pitch Ball Grid Array (FBGA)

502

1.0

27 x 27

2.60

Notes:

1.

For mass, refer to the MDDS files (see Table 66).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC024T-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XA2S100E-6TQ144I | IC FPGA SPARTAN-IIE 144TQFP |

| 24LC024-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| 24LC025-E/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XC6SLX9-L1FT256I | IC FPGA SPARTAN 6 256FTGBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S5000-4FG1156C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156CES | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG1156I | 制造商:Xilinx 功能描述: |

| XC3S5000-4FG676C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

| XC3S5000-4FG676I | 制造商:Xilinx 功能描述:FPGA SPARTAN-3 5M GATES 74880 CELLS 630MHZ 1.2V 676FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。