- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372925 > XPC755BRX400LE Microprocessor PDF資料下載

參數(shù)資料

| 型號: | XPC755BRX400LE |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 11/52頁 |

| 文件大小: | 1274K |

| 代理商: | XPC755BRX400LE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

MOTOROLA

MPC755 RISC Microprocessor Hardware Specifications

11

Electrical and Thermal Characteristics

1.4.2

AC Electrical Characteristics

This section provides the AC electrical characteristics for the MPC755. After fabrication, functional parts

are sorted by maximum processor core frequency as shown in Section 1.4.2.1, “Clock AC Specifications,”

and tested for conformance to the AC specifications for that frequency. The processor core frequency is

determined by the bus (SYSCLK) frequency and the settings of the PLL_CFG[0:3] signals. Parts are sold

by maximum processor core frequency; see Section 1.10, “Ordering Information.”

1.4.2.1

Clock AC Specifications

Table 8 provides the clock AC timing specifications as defined in Figure 3.

Nap Mode

1.0

Sleep Mode

470

Maximum

1.0

1.0

1.0

W

1, 2

Maximum

460

470

470

mW

1, 2

Sleep Mode (PLL and DLL Disabled)

340

430

Typical

Maximum

Notes:

1. These values apply for all valid processor bus and L2 bus ratios. The values do not include I/O supply power

(OV

DD

and L2OV

DD

) or PLL/DLL supply power (AV

DD

and L2AV

DD

). OV

DD

and L2OV

DD

power is system

dependent, but is typically <10% of V

DD

power. Worst case power consumption for AV

DD

= 15 mW and L2AV

DD

= 15 mW.

2. Maximum power is measured at nominal V

DD

(see Table 4) while running an entirely cache-resident, contrived

sequence of instructions which keep the execution units, with or without AltiVec, maximally busy.

3. Typical power is an average value measured at the nominal recommended V

DD

(see Table 3) and 65

°

C in a

system while running a typical code sequence.

340

430

340

430

340

430

mW

mW

1, 3

1, 2

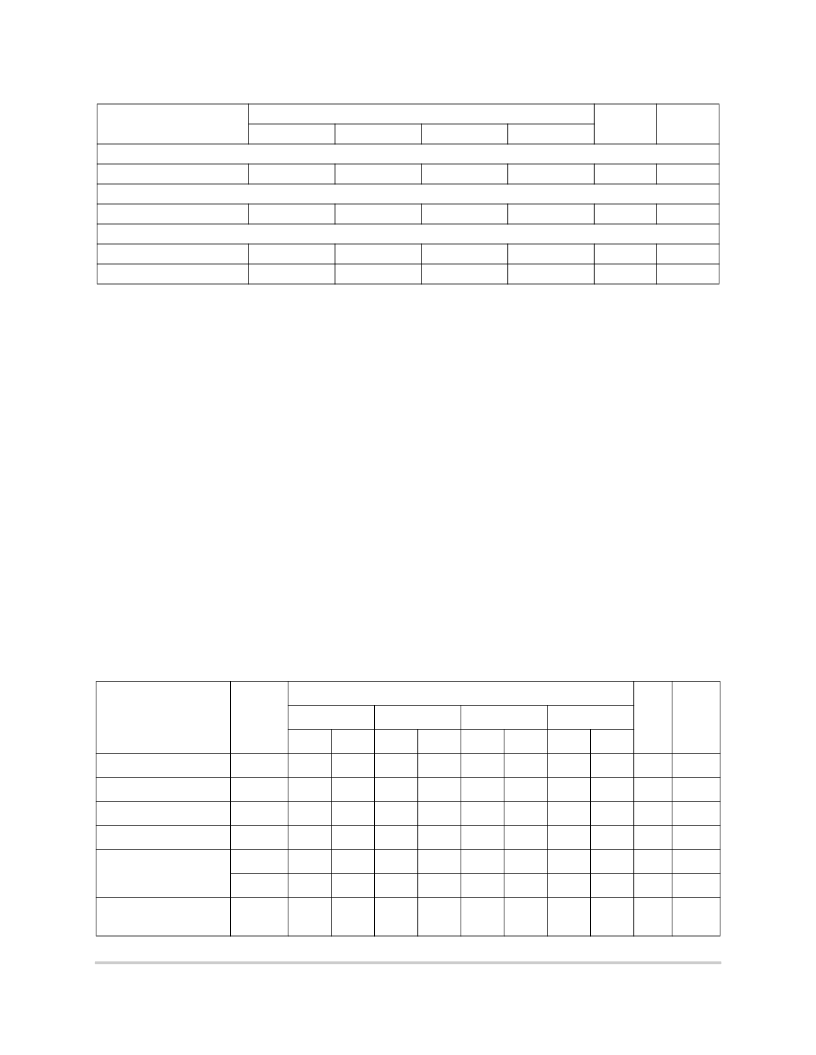

Table 8. Clock AC Timing Specifications

At recommended operating conditions (see Table 3)

Characteristic

Symbol

Maximum Processor Core Frequency

Unit

Notes

300 MHz

350 MHz

400 MHz

450 MHz

Min

Max

Min

Max

Min

Max

Min

Max

Processor frequency

f

core

200

300

200

350

200

400

200

450

MHz

1

VCO frequency

f

VCO

400

600

400

700

400

800

400

900

MHz

1

SYSCLK frequency

f

SYSCLK

25

100

25

100

25

100

25

100

MHz

1

SYSCLK cycle time

t

SYSCLK

10

40

10

40

10

40

10

40

ns

SYSCLK rise and fall

time

t

KR

, t

KF

—

2.0

—

2.0

—

2.0

—

2.0

ns

2

t

KR

, t

KF

—

1.4

—

1.4

—

1.4

—

1.4

ns

2

SYSCLK duty cycle

measured at OV

DD

/2

t

KHKL

/

t

SYSCLK

40

60

40

60

40

60

40

60

%

3

Table 7. Power Consumption for MPC755 (continued)

Processor (CPU) Frequency

350 MHz

Unit

Notes

300 MHz

400 MHz

450 MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XPC750EC | XPC750P/D XPC750P RISC Microprocessor Hardware Specifications |

| XPC801ZP25 | Microprocessor |

| XPC801ZP40 | Microprocessor |

| XPC821ZP40 | Microprocessor |

| XPC823ZP25 | Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XPC801ZP25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| XPC801ZP40 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| XPC821ZP40 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| XPC823CVR66B2T | 功能描述:IC MPU POWERQUICC 66MHZ 256-PBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:MPC8xx 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| XPC823CZC66A | 制造商:Freescale Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。