- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359147 > MC72000 (飛思卡爾半導(dǎo)體(中國)有限公司) Integrated Bluetooth Radio PDF資料下載

參數(shù)資料

| 型號(hào): | MC72000 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | Integrated Bluetooth Radio |

| 中文描述: | 集成藍(lán)牙無線 |

| 文件頁數(shù): | 113/156頁 |

| 文件大?。?/td> | 1782K |

| 代理商: | MC72000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁當(dāng)前第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁

MOTOROLA

MC72000

Advance Information Data Sheet

Go to: www.freescale.com

113

The operation of clearing the TE bit disables the transmitter after completion of transmission of the current

data word. Setting the TE bit again enables transmission of the next word. During the time that TE=0, the

STXD signal is tri-stated. The TE bit should be cleared after the TDE bit is set to ensure that all pending

data is transmitted.

To summarize, the network mode transmitter generates interrupts every time slot (unless the TSM registers

are used) and requires the DSP program to respond to each time slot. These responses may be one of the

following:

Write the data register with data to enable transmission in the next time slot.

Write the time slot register to disable transmission in the next time slot.

Do nothing—transmit underrun occurs at the beginning of the next time slot and the previous data

is re-transmitted.

7.4.6.1.2.2

Network Mode Receive

The receiver portion of the SSI is enabled when both the SSIEN and the RE bits in the SCR2 are set.

However, when the RE bit is set, the receiver is enabled only after detection of a new frame boundary.

Software has to find the start of the next frame (by checking the RFS bit in the SCSR register). A normal

start-up sequence for receive operation is to do the following steps:

1. Set the SCSR, SRXCR, SCR2, and SOR registers to select network mode operation, define

the receive clock, receive frame sync, and frame structure required for proper system

operation.

2. Enable SSI (SSIEN = 1).

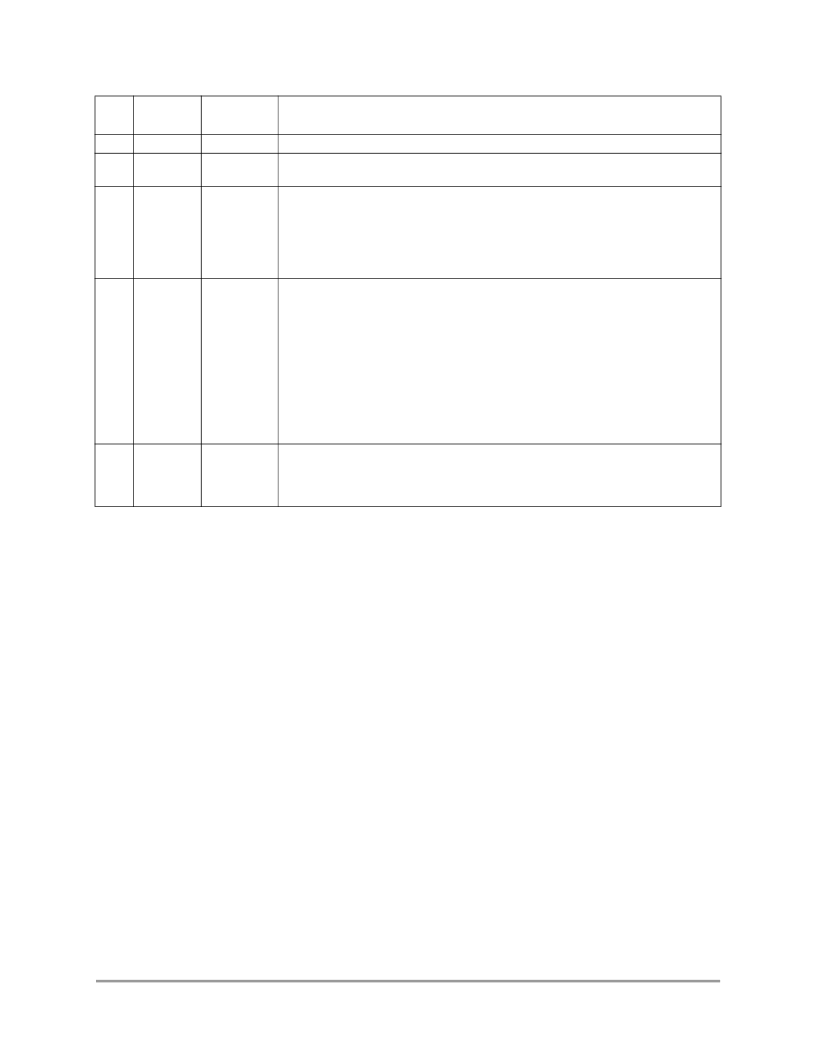

Table 56. Notes for Transmit Timing in Figure 74

Note

Source

Signal

Destination

Signal

Description

1

Example of a 5 time-slot frame, transmitting in time-slots 0 and 3.

Example with word-length frame sync and standard timing (TFSI=0, TFSL=0,

TEFS=0). Frame timing begins with the rising edge of STFS.

This flag is set at the beginning of each word to indicate that another data word

should be supplied by the software. If the transmit interrupt is enabled, the

processor is interrupted to request the data. The flag (and interrupt) are cleared

when data is written to either the STX or STSR registers (see Section 7.4.9.2,

“Description of Interrupt Operation” for a complete description of interrupt

processing).

On each word clock boundary a decision is made concerning what to transmit on

the next time-slot.

If the STSR register was written during the previous time-slot, the STXD pin is tri-

stated. If the STSR register was NOT written during the previous time-slot, the

contents of the STX register is transferred to the TXSR register and this data is

shifted out. If the STX register has not been written in the previous time-slot, the

previous data is reused.

If neither of these registers were written in the previous time-slot, the TUE status

bit will be set and the hardware will operate as if the STX register had been written.

The STXD pin will be enabled and the contents of the STX will be transmitted

again. Note that this may lead to drive conflicts on the transmit data line.

On active time-slots, the TXSR register contents are shifted out on the STXD pin,

one bit per rising edge of STCK.

On inactive time-slots, the STXD pin is tri-stated so it can be driven by another

device.

2

STFS

3

TDE status

flag and

interrupt

4

STX/STSR

register

TXSR

register

5

TXSR

register

STXD pin

F

Freescale Semiconductor, Inc.

For More Information On This Product,

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC7445ARX1000LF | RISC Microprocessor Hardware Specifications |

| MC7445ARX1000LG | RISC Microprocessor Hardware Specifications |

| MC7447A | PowerPC microprocessor |

| MC7447AHX1000NB | PowerPC microprocessor |

| MC7447AHX1167NB | PowerPC microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC7220C-100M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20CORE 100M 制造商:pro-power 功能描述:CABLE, DEF 7-2-20C, 20CORE, 100M 制造商:pro-power 功能描述:CABLE, DEF 7-2-20C, 20CORE, 100M; Reel Length (Imperial):328ft; Reel Length (Metric):100m; No. of Conductors:20; Voltage Rating:440V; No. of Strands x Strand Size:7 x 0.2mm; Conductor Area CSA:0.22mm2; Jacket Colour:Black; Jacket ;RoHS Compliant: Yes |

| MC7220C-100M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20 CORE 100M |

| MC7220C-25M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20CORE 25M 制造商:pro-power 功能描述:CABLE, DEF 7-2-20C, 20CORE, 25M |

| MC7220C-25M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20 CORE 25M |

| MC7225C-25M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-25C 25CORE 25M 制造商:pro-power 功能描述:MULTICORE, 25, 7/0.2MM, 25M, BLACK 制造商:pro-power 功能描述:CABLE, DEF 7-2-25C, 25CORE, 25M 制造商:PRIVATE LABEL 功能描述:CABLE, DEF 7-2-25C, 25CORE, 25M, Reel Length (Imperial):82ft, Reel Length (Metri |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。