- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄368232 > PSD813FH Field Programmble Microcontroller Peripherals With Flash Memory(帶閃存的現(xiàn)場(chǎng)可編程微控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | PSD813FH |

| 英文描述: | Field Programmble Microcontroller Peripherals With Flash Memory(帶閃存的現(xiàn)場(chǎng)可編程微控制器) |

| 中文描述: | 場(chǎng)可編程微控制器外圍設(shè)備與快閃記憶體(帶閃存的現(xiàn)場(chǎng)可編程微控制器) |

| 文件頁(yè)數(shù): | 42/83頁(yè) |

| 文件大?。?/td> | 369K |

| 代理商: | PSD813FH |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)

PSD813FN/FH

Prelimnary

42

VM Reg Bit 1

RD_EN

VM Reg Bit 0

PSEN_EN

Run-Time Mode

0

0

1

1

0

1

0

1

Separate Space Mode (default at reset)

Combined Program Space Mode

Combined Data Space Mode

Combined Space Mode

Table 25. VM Register

NOTE:

Bits 6-2 are not used. Use of bit 7 is described in the Peripheral I/O mode section.

Memory Select for 8031 Microcontrollers

The 8031 family of microcontrollers have a separate address space for program memory

(enabled by PSEN) and data memory (enabled by RD). Normally, the Boot EPROM would

lie in program address space and the SRAM would lie in data address space. The

PSD813FN/FH allows the Boot EPROM and SRAM address space to reside in program

space, data space or both. This flexibility enables several system designs. For example, if

the user desires to execute a program that resides in SRAM, the SRAM would have to

occupy program address space (enabled by PSEN). Likewise, the user may devote a block

of Boot EPROM to contain data lookup tables, requiring the Boot EPROM to occupy data

address space (enabled by RD).

The internal PSD Boot EPROM and SRAM each have their own output enable.

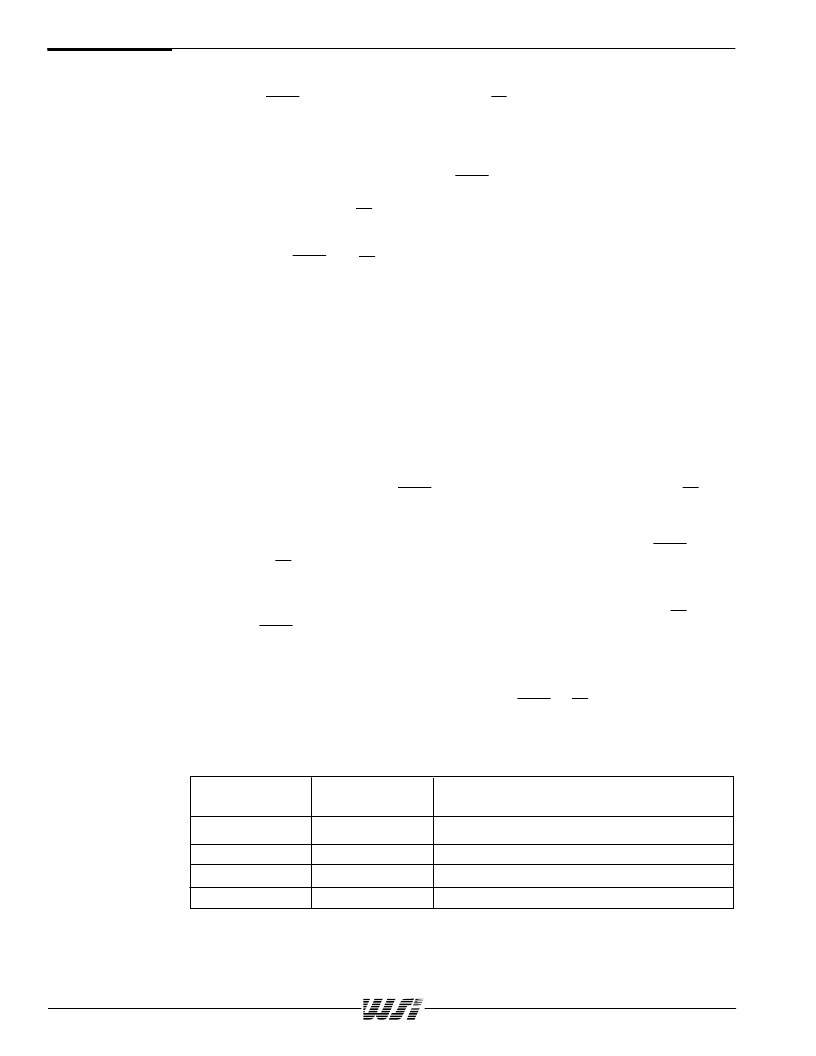

Combinations of PSEN and RD drive these output enables and are determined by bits set

at Run-Time by the MCU in the VM register (see Table 25). The schematic representation

can be seen in Figure 19 and the action of bit 0 and bit 1 of the VM register is shown.

There are four modes of operation that can be selected by the MCU at Run-Time as shown

in Table 25. All of these modes assume there are no overlapping address assignments for

blocks of Boot EPROM and SRAM. These blocks of memory may reside in the same 64K

program or data space, but not share any physical addresses within the 64K. Example 1:

Boot EPROM block 0 and SRAM cannot both start at address 0000. Example 2: Boot

EPROM block 2 in program space and Boot EPROM block 3 in data space cannot both

start at address 8000).

J

Separate Space Mode

Program memory space is separate from data memory space. This default state ties the

Boot EPROM output enable to PSEN only, and ties the SRAM output enable to RD only.

J

Combined ProgramSpace Mode

This mode allows the SRAM to reside in program space (to be enabled by PSEN

as well as RD).

J

Combined Data Space Mode

This mode allows the Boot EPROM to reside in data space (to be enabled by RD as

well as PSEN).

J

Combined Space Mode

This mode allows both the Boot EPROM and SRAM to reside in either program space

or data space (either memory may be accessed by PSEN or RD).

Memory Blocks

(cont.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD82 | Three Phase Rectifier Bridges |

| PSD834F2V | Flash PSD, 3.3V Supply, for 8-bit MCUs 2 Mbit + 256 Kbit Dual Flash Memories and 64 Kbit SRAM(2M位+256K位雙路閃速存儲(chǔ)器和64K位靜態(tài)RAM,閃速PSD,3.3V電源,用于8位MCU.) |

| PSD834F2 | Flash In-System Programmable (ISP) Peripherals For 8-bit MCUs(用于8位MCUs的閃速I(mǎi)SP外圍) |

| PSD835G2 | Configurable Memory System on a Chip for 8-Bit Microcontrollers(8位微控制器片上存儲(chǔ)器可編程外設(shè)) |

| PSD835G2 | 100V 100kRad Hi-Rel Single N-Channel TID Hardened MOSFET in a TO-254AA Tabless package; Similar to IRHMJ57160 with optional Total Dose Rating of 1000kRads |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD813FH-15J | 制造商:WSI 功能描述: |

| PSD813FH-90J | 制造商:WSI 功能描述: |

| PSD813FN-15J | 制造商:WSI 功能描述: |

| PSD833F2-90J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD833F2-90JI | 功能描述:SPLD - 簡(jiǎn)單可編程邏輯器件 5.0V 1M 90ns RoHS:否 制造商:Texas Instruments 邏輯系列:TICPAL22V10Z 大電池?cái)?shù)量:10 最大工作頻率:66 MHz 延遲時(shí)間:25 ns 工作電源電壓:4.75 V to 5.25 V 電源電流:100 uA 最大工作溫度:+ 75 C 最小工作溫度:0 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:DIP-24 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。