- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365967 > TSB12LV01BPZ FPGA (Field-Programmable Gate Array) PDF資料下載

參數(shù)資料

| 型號(hào): | TSB12LV01BPZ |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 總線控制器 |

| 文件頁(yè)數(shù): | 25/106頁(yè) |

| 文件大小: | 605K |

| 代理商: | TSB12LV01BPZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)

2

–

9

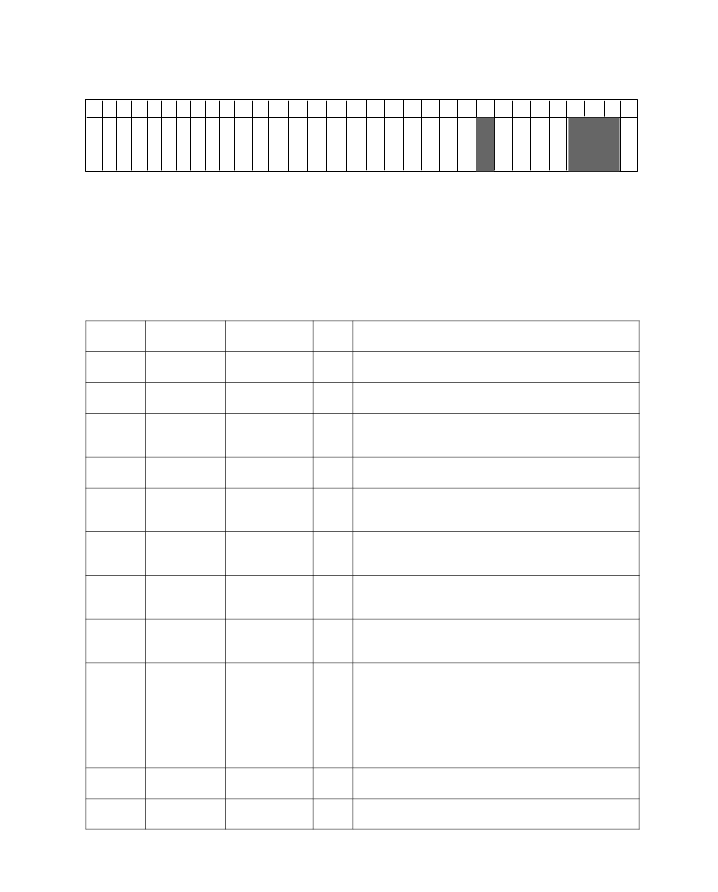

2.2.4

Interrupt/Interrupt Mask Register at 0Ch and 10h

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

A

29 30 31

28

P

S

S

R

P

S

C

C

C

C

C

I

A

S

H

I

A

P

C

D

R

A

T

M

D

F

L

The interrupt and interrupt mask register work in tandem to inform the host bus interface when the state of

the TSB12LV32 changes. The interrupt register is at 0Ch, the interrupt mask register is at 10h. The interrupt

register powers up all 0s, however, the interrupt mask register powers up with the INT and the MCERROR

bit set, i.e. 8000_1000h. The mask bits allows individual control for each interrupt. A 1 in the mask bit field

allows the corresponding interrupt in the interrupt register to be generated. Once an interrupt is generated

it must be cleared by writing a 1 to the bit in the interrupt register. For testing, each interrupt bit can be set

manually. This is done by first setting the REGRW bit at20h and then setting the individual interrupt bit. This

is also true for bit 0 at0Ch. In this test mode, the interrupt mask register is not used and has no effect.

BIT

NUMBER

BIT NAME

FUNCTION

DIR

DESCRIPTION

0

INT

Interrupt

R/W

INT contains the value of all interrupt and interrupt mask bits

ORed together

1

PHINT

Phy chip

interrupt

R/W

When PHINT is set, the Phy has signalled an interrupt

through the Phy interface

2

PHRRX

Phy register

information

received

R/W

When PHRRX is set, a register value has been transferred to

the Phy access register (offset 24h) from the Phy interface

3

PHRST

Phy reset

started

R/W

When PHRST is set, a Phy-LLC reconfiguration has started

(1394 bus reset)

4

SELFIDEND

Self-ID

validated

R/W

Self-ID end. This bit is set at the end of the self-ID reporting

process. When this bit is set, the contentF of the bus reset

CFR at34h is valid.

5

ATSTARTED

Asynchronous

transfer started

R/W

Asynchronous transfer started. Activated when the bus has

been granted and the first quadlet from the FIFO is about to

be popped from the ATF.

6

RXGRFPKT

GRF packet

received

R/W

Receive packet to GRF. This bit is set whenever a complete

packet has been confirmed into the GRF (asynchronous or

isochronous).

7

CMDRST

CSR register

reset request

R/W

If CMDRST is set, the receiver has been sent a quadlet write

request to the Reset_Start CSR register(target address is

FFFF_F000_000Ch)

8

DMERROR

Data Mover

error

R/W

DM error. This bit will be set whenever there is an error in the

DM stream. For transmit, if the DM port is configured for byte

access and the speed code in the DM control register or the

asynchronous header register is set for 400 Mbps then this

bit will be set. Under this condition DMEN will be reset to 0

preventing further transmit. For receive this bit will be set if

there is a header or data CRC error or if the DM port is config-

ured for byte access and the data is received at 400 Mbps.

9

RXDMPKT

Data Mover

packet receive

R/W

Receive packet to DM. This bit is set whenever a packet is

received to the DM port.

10

SELFIDER

Self-ID packet

error

R/W

Set if an error in the self-ID quadlet/packet has been de-

tected.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB12LV26-EP | 672-pin FineLine BGA |

| TSB12LV22PZP | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZ | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12LV01BPZT | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01BPZTG4 | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01PZ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB12LV21 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394 LINK LAYER CONTROLLER |

| TSB12LV21A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 BUS TO PCI BUS INTERFACE |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。