- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365967 > TSB12LV01BPZ FPGA (Field-Programmable Gate Array) PDF資料下載

參數(shù)資料

| 型號: | TSB12LV01BPZ |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 總線控制器 |

| 文件頁數(shù): | 93/106頁 |

| 文件大小: | 605K |

| 代理商: | TSB12LV01BPZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當前第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

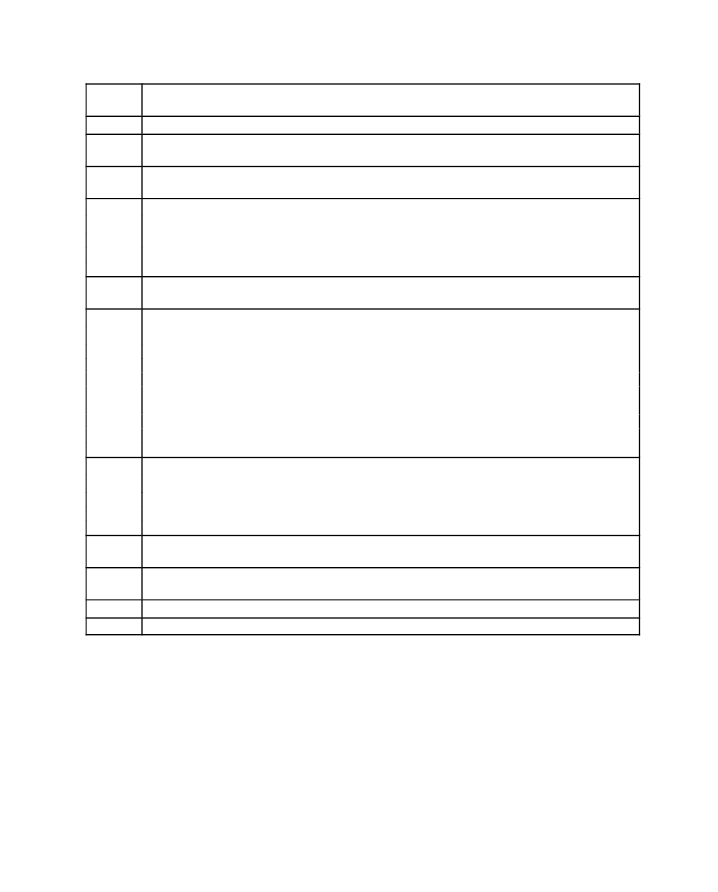

7

–

15

Table 7

–

15. Phy Self-ID Packet Fields

FIELD

NAME

DESCRIPTION

10

The 10 field is the self-ID packet identifier.

L

If set, this node has an active link and transaction layers. In discrete Phy implementations, this shall be the

logical AND of Link_active and LPS active.

gap_cnt

The gap_cnt field contains the current value for the current node PHY_CONFIGURATION.gap_count

field.

sp

The sp field contains the Phy speed capability. The code is:

00

01

10

11

98.304 Mbits/s

98.304 Mbits/s and 196.608 Mbits/s

98.304 Mbits/s 196.608 Mbits/s, and 393.216 Mbits/s

Extended speed capabilities reported in Phy register 3

c

If set and the link_active flag is set, this node is contender for the bus or isochronous resource manager as

described in clause 8.4.2 of IEEE Std 1394

–

1995.

pwr

Power consumption and source characteristics:

000

001

010

011

100

Node does not need power and does not repeat power.

Node is self-powered and provides a minimum of 15W to the bus.

Node is self-powered and provides a minimum of 30W to the bus.

Node is self-powered and provides a minimum of 45W to the bus.

Node may be powered from the bus and is using up to 3W. No additional power is needed to enable

the link

.

Reserved for future standaraization.

Node is powered from the bus and is using up to 3W. An additional 3W is needed to enable the link

.

Node is powered from the bus and is using up to 3W. An additional 7W is needed to enable the link

.

101

110

111

p0

–

p15

The p0

–

p15 field indicates the port connection status. The code is:

00

01

10

11

Not present on the current Phy

Not connected to any other Phy

Connected to the parent node

Connected to the child node

i

If set, this node initiated the current bus reset (i.e., it started sending a bus_reset signal before it received

one)

.

m

If set, another self-ID packet for this node will immediately follow (i.e., if this bit is set and the next Self-ID

packet received has a different Phy_ID, the a self-ID packet was lost)

n

Extended self-ID packet sequence number

rsv

There is no way to ensure that exactly one node has this bit set. More than one node can be requesting a bus reset at

the same time.

The link is enabled by the link-on Phy packet described in clause 7.5.2 of the IEEE 1394.a spec.; this packet may also

enable application layers.

Reserved and set to all zeros

相關PDF資料 |

PDF描述 |

|---|---|

| TSB12LV26-EP | 672-pin FineLine BGA |

| TSB12LV22PZP | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZ | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12LV01BPZT | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01BPZTG4 | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01PZ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB12LV21 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394 LINK LAYER CONTROLLER |

| TSB12LV21A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 BUS TO PCI BUS INTERFACE |

發(fā)布緊急采購,3分鐘左右您將得到回復。