- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365967 > TSB12LV01BPZ FPGA (Field-Programmable Gate Array) PDF資料下載

參數(shù)資料

| 型號(hào): | TSB12LV01BPZ |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 總線控制器 |

| 文件頁(yè)數(shù): | 70/106頁(yè) |

| 文件大小: | 605K |

| 代理商: | TSB12LV01BPZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)當(dāng)前第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)

5

–

14

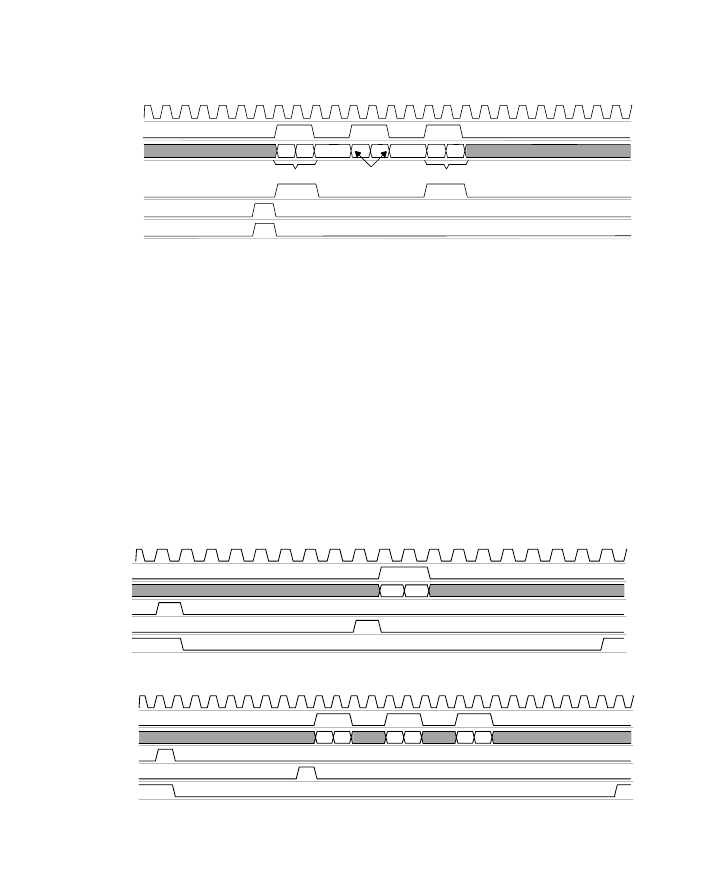

Figure 5

–

19 shows the timing diagram at 200 Mbps when the received packet contains only one quadlet

of payload.

Packet payload

0000

DMCLK

DMRW

DMD[0:15]

PKTFLAG

DMDONE

DMPRE

0000

Trailer quadlet

Header quadlet

Figure 5

–

19. Isochronous Receive With Header and Trailer at 200 Mbps

5.2.5

Asynchronous Packet Transmit With Automatic Header Insertion

Upon receiving a high on DMREADY, the following sequence of operations are performed:

Step 1:

DMDONE will be asserted low (deactivated) at the next DMCLK cycle.

Step 2:

The data mover will take the headers that have been loaded into the header0

–

header3

registers and request the link core to transmit the data onto the 1394 bus.

Step 3:

The link core will fetch the headers from the header0

–

header3 registers.

Step 4:

DMPRE will pulse for one DMCLK cycle before the first data quadlet is sent.

Step 5:

The data mover will then begin to fetch the data payload by asserting DMRW high.

Step 6:

When the link core has fetched the last data quadlet, the data mover waits until the

destination node returns an

ack_complete

immediate response. If an

ack_complete

is not

received, the data mover will assert DMERROR high and become disabled.

Figure 5

–

20 and Figure 5

–

21 show the timing diagram for this mode for the quadlet transmit and the block

transmit cases, respectively. For simplicity, a data block size of three quadlets was selected in Figure 5

–

20.

Figure 5

–

22 shows the block transmit case at 400 Mbps.

DMCLK

DMRW

DMD[0:15]

DMREADY

DMPRE

DMDONE

Figure 5

–

20. Asynchronous Quadlet Transmit With Automatic Header Insertion

DMCLK

DMRW

DMD[0:15]

DMREADY

DMPRE

DMDONE

Figure 5

–

21. Asynchronous Block Transmit With Automatic Header Insertion at 200 Mbps

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB12LV26-EP | 672-pin FineLine BGA |

| TSB12LV22PZP | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZ | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12LV01BPZT | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01BPZTG4 | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01PZ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB12LV21 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394 LINK LAYER CONTROLLER |

| TSB12LV21A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 BUS TO PCI BUS INTERFACE |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。