- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365967 > TSB12LV32-EP IC APEX 20KE FPGA 100K 324-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | TSB12LV32-EP |

| 英文描述: | IC APEX 20KE FPGA 100K 324-FBGA |

| 中文描述: | 軍事增強(qiáng)塑料電機(jī)及電子學(xué)工程師聯(lián)合會(huì)1394-1995和P1394a兼容通用鏈路層控制器 |

| 文件頁數(shù): | 24/106頁 |

| 文件大?。?/td> | 605K |

| 代理商: | TSB12LV32-EP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

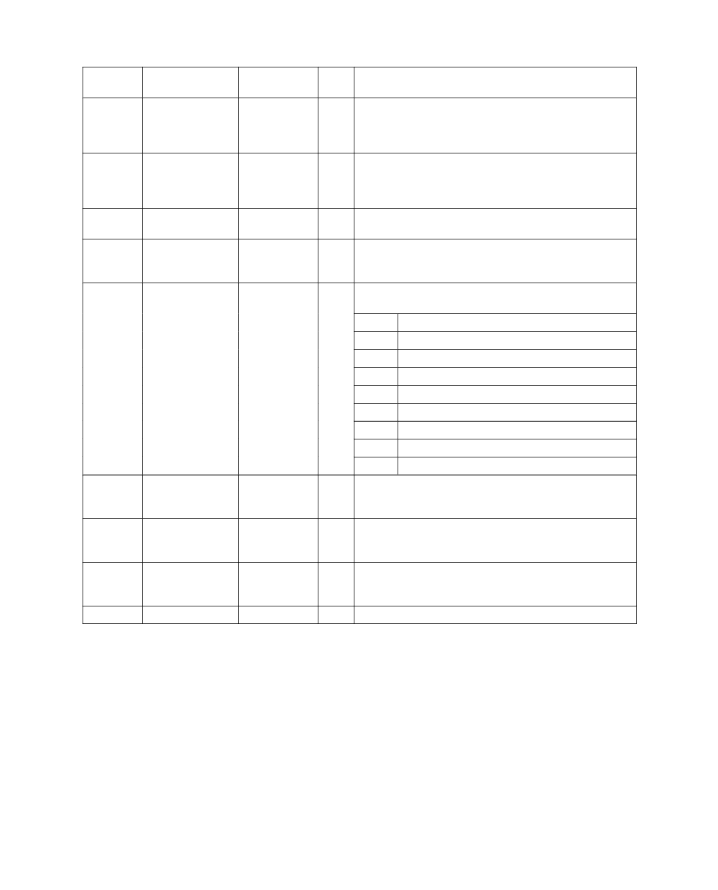

2

–

8

BIT

NUMBER

DESCRIPTION

DIR

FUNCTION

BIT NAME

20

CYMAS

Cycle Master

R/W

When CYMAS is set and the TSB12LV32 is attached to the

root Phy, the cyclemaster function is enabled. When the

cycle_count field of the cycle timer register increments, the

transmitter sends a cycle-start packet.

21

CYSRC

Cycle Source

R/W

When CYSRC is set, the cycle_count field increments and

the cycle_offset field resets for each positive transition of

CYCLEIN. When CYSRC is cleared, the cycle_count field

increments when the cycle_offset field rolls over.

22

CYTEN

Cycle timer

enable

R/W

When CYTEN is set, the cycle_offset field increments.

23

CLRSIDER

Self-ID

error-code

clear

W

When CLRSIDER is set, the SIDERCODE field (bits 24

–

27)

is cleared.This bit clears itself.

24

–

27

SIDERCODE

Self-ID error

code

R

SIDERCODE contains the error code of the first Self-ID

Error. The error code is as follows:

0000

No error

0001

Last self-ID received was not all child ports

0010

Received Phy ID in self-ID not as expected

0011

Quadlet not inverted (phase error)

0100

Phy ID sequence error (two or more gaps in IDs)

0101

Phy ID sequence error (large gap in IDs)

0110

Phy ID error within packet

0111

Quadlet not the inversion of the prior quadlet

1000

Reserved

28

CMAUTO

Auto set cycle

master

R/W

When CMAUTO is high, the TSB12LV32 automatically

enables CYMAS when the this node becomes the root

following a bus reset.

29

IRP1EN

IR port 1

enable

R/W

When IRP1EN is set, the receiver accepts isochronous

packets when the channel number matches the value in the

IR port1 field at18h

30

IRP2EN

IR port 2

enable

R/W

When IRP2EN is set, the receiver accepts isochronous

packets when the channel number matches the value in the

IR Port2 field at18h

31

RESERVED

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB12LV01B-EP | FPGA (Field-Programmable Gate Array) |

| TSB12LV01BPZ | FPGA (Field-Programmable Gate Array) |

| TSB12LV26-EP | 672-pin FineLine BGA |

| TSB12LV22PZP | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZ | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12LV32I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 and P1394a Compliant General-Purpose Link-Layer Controller |

| TSB12LV32IPZ | 功能描述:1394 接口集成電路 General-Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV32IPZEP | 制造商:Texas Instruments 功能描述:1394 I-TEMP 1394 GENERAL-PURPOSE LINK LAYER CONTROLLER (GP2L - Rail/Tube |

| TSB12LV32IPZG4 | 功能描述:1394 接口集成電路 General Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV32PZ | 功能描述:1394 接口集成電路 General-Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。