- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365967 > TSB12LV32-EP IC APEX 20KE FPGA 100K 324-FBGA PDF資料下載

參數(shù)資料

| 型號: | TSB12LV32-EP |

| 英文描述: | IC APEX 20KE FPGA 100K 324-FBGA |

| 中文描述: | 軍事增強塑料電機及電子學工程師聯(lián)合會1394-1995和P1394a兼容通用鏈路層控制器 |

| 文件頁數(shù): | 52/106頁 |

| 文件大小: | 605K |

| 代理商: | TSB12LV32-EP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

3

–

15

Number

SLLA021.pdf

ENDIANNESS AND THE TSB12LV41 (MPEG2LYNX) MICROPROCESSOR

INTERFACE

for a detailed description of endianness.

The pin settings for all the swapping operation are shown in Table 3

–

3. Note that in performing the byte

swapping operation in the little-endian mode, only the two least significant bits of the 32-bit address inside

are involved. This is because there is a total of four bytes associated with the swapping operation.

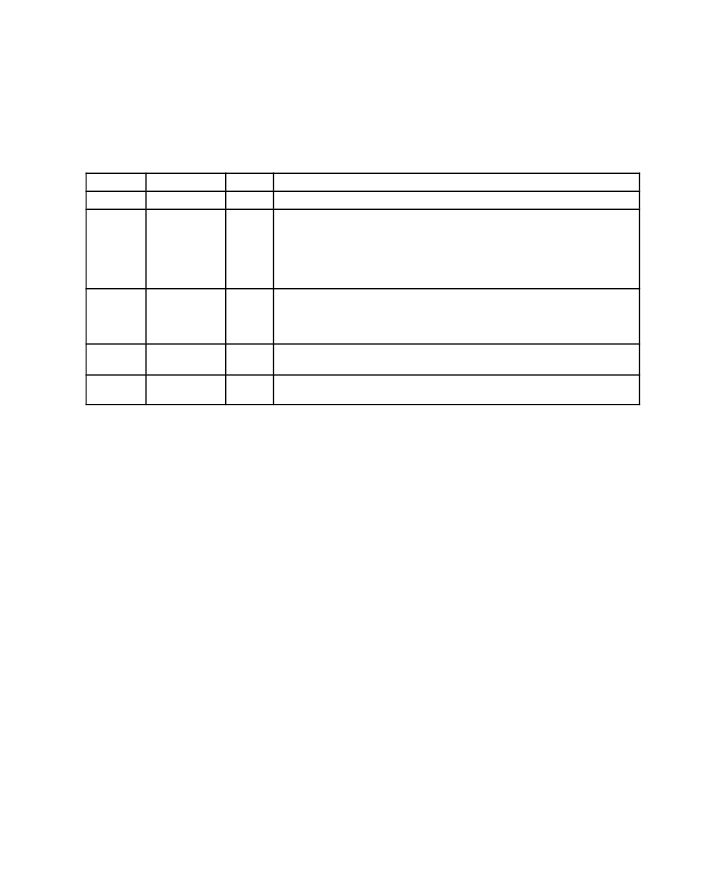

Table 3

–

3. Endian Swapping Operation

LENDIAN

M8BIT/SIZ0

MDINV

DESCRIPTION

0

X

X

Big endian mode, no manipulation on byte address and data bytes

1

1

(8-bits wide)

1

Little endian data invariance mode, swap the low order 2 bit address:

External low order 2-bit address Internal low order 2-bit address

Byte Address 00

Byte Address 01

Byte Address 00

Byte Address 11

Little endian data invariance mode, swap the low order 2 bit address:

External low order 2-bit address Internal low order 2-bit address

Word Address 00

Word Address 10

16-bit little endian address invariance mode, swap data between MD[0:7] and

MD[8:15].

Byte Address 11

Byte Address 10

Byte Address 11

Byte Address 00

1

01

(16-bits wide)

1

Word Address 10

Word Address 00

1

1

0

1

1

0

8-bit little endian address invariance mode, no manipulation on byte address

and data bytes.

Since the TSB12LV32

’

s microprocessor interface is either 8 bits or 16 bits wide, but the internal configuration

registers are 32 bits wide, a byte stacking (for writes) and a byte unstacking (for reads) operation must be

performed on the data bus. For little endian processors, the TSB12LV32 can perform the swapping of bytes

on the data bus required to allow both the processor and the TSB12LV42 to interpret the data the same.

There are two methods of swapping the data bytes, address invariant and data invariant. Both of these

methods are described below.

NOTE:

For the host processor to work correctly with the TSB12LV32, users

must

correctly

connect the address and data busses of their microprocessor to the TSB12LV32

’

s

microprocessor port. Users must connect the MSB (most significant bit) of their

address/data bus to the address/data MSB of the TSB12LV32. This must be done

regardless of bit number labeling or which type of endianness their microprocessor

uses.

3.3.5.2

Figure 3

–

17 shows a little endian data invariant system design example. In this system, the actual value of

the data as it was stored in the processor

’

s memory is preserved. Data invariant designs do not preserve

the addresses when mapping between endian domains. If the data represents an integer, it is interpreted

the same by both systems. If the data represents a string, an array, or some other type of byte indexed

structure, it is interpreted differently by both systems.

Data Invariant System Design

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB12LV01B-EP | FPGA (Field-Programmable Gate Array) |

| TSB12LV01BPZ | FPGA (Field-Programmable Gate Array) |

| TSB12LV26-EP | 672-pin FineLine BGA |

| TSB12LV22PZP | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZ | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12LV32I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 and P1394a Compliant General-Purpose Link-Layer Controller |

| TSB12LV32IPZ | 功能描述:1394 接口集成電路 General-Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV32IPZEP | 制造商:Texas Instruments 功能描述:1394 I-TEMP 1394 GENERAL-PURPOSE LINK LAYER CONTROLLER (GP2L - Rail/Tube |

| TSB12LV32IPZG4 | 功能描述:1394 接口集成電路 General Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV32PZ | 功能描述:1394 接口集成電路 General-Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。