- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371362 > 20736 Enhanced Am486DX Family Data Sheet? 1.87MB (PDF) PDF資料下載

參數(shù)資料

| 型號(hào): | 20736 |

| 英文描述: | Enhanced Am486DX Family Data Sheet? 1.87MB (PDF) |

| 中文描述: | 增強(qiáng)Am486DX系列數(shù)據(jù)手冊(cè)? 1.87MB(PDF格式) |

| 文件頁(yè)數(shù): | 42/66頁(yè) |

| 文件大小: | 1923K |

| 代理商: | 20736 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

42

Enhanced Am486DX Microprocessor Family

P R E L I M I N A R Y

6.3.4

When SMI is recognized on an instruction boundary, the

CPU core first sets the SMIACT signal Low, indicating

to the system logic that accesses are now being made

to the system-defined SMRAM areas. The CPU then

writes its state to the state save area in the SMRAM.

The state save area starts at SMBASE + [8000h +

7FFFh]. The default CS Base is 30000h; therefore, the

default state save area is at 3FFFFh. In this case, the

CS Base is also referred to as the SMBASE.

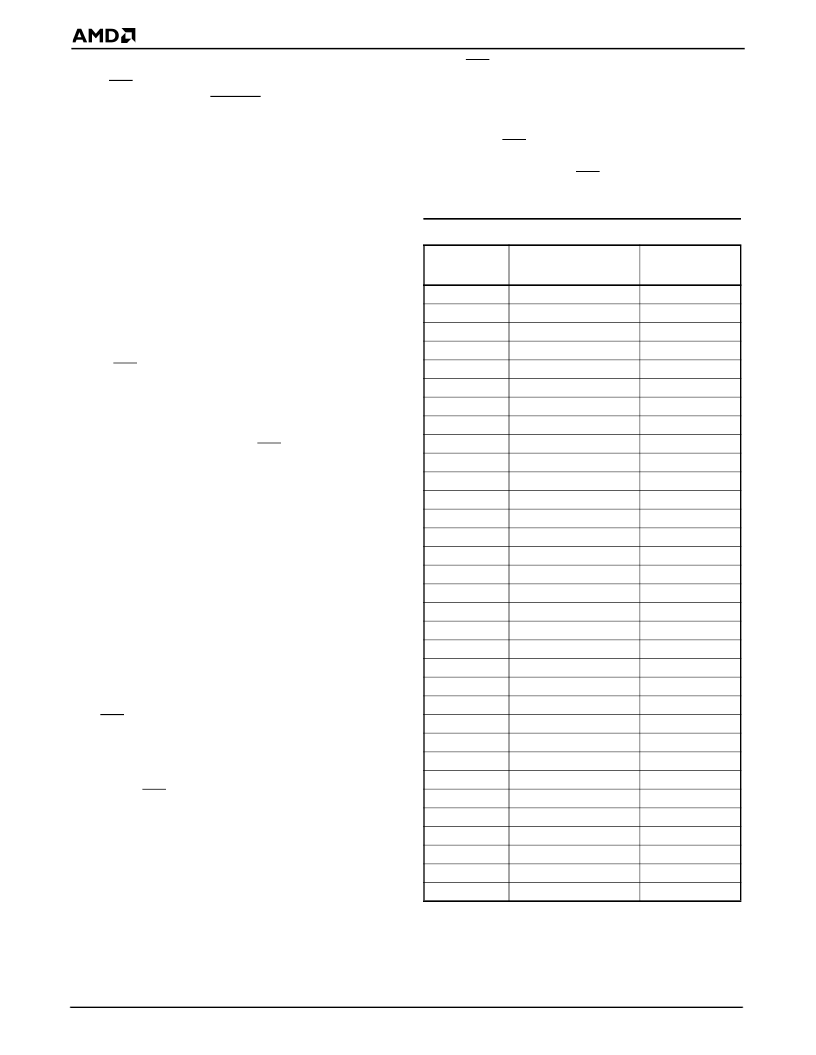

SMRAM State Save Map

If the SMBASE relocation feature is enabled, the

SMRAM addresses can change. The following formula

is used to determine the relocated addresses where the

context is saved: SMBASE + [8000h + Register Offset],

where the default initial SMBASE is 30000h and the

Register Offset is listed in Table 11. Reserved spaces

are for new registers in future CPUs. Some registers in

the SMRAM state save area may be read and changed

by the SMI handler, with the changed values restored

to the processor register by the RSM instruction. Some

register images are read-only, and must not be modified.

(Modifying these registers results in unpredictable

behavior.) The values stored in the “reserved” areas

may change in future CPUs. An SMI handler should not

rely on values stored in a reserved area.

The following registers are written out during SMSAVE

mode to the RESERVED memory locations (7FA7h–

7F98h, 7F93h–7F8Ch, and 7F87h–7F08h), but are not

visible to the system software programmer:

I

DR3–DR0

I

CR2

I

CS, DS, ES, FS, GS, and SS hidden descriptor

registers

I

EIP_Previous

I

GDT Attributes and Limits

I

IDT Attributes and Limits

I

LDT Attributes, Base, and Limits

I

TSS Attributes, Base, and Limits

If an SMI request is issued to power down the CPU, the

values of all reserved locations in the SMM state save

area must be saved to non-volatile memory.

The following registers are not automatically saved and

restored by SMI and RSM:

I

TR7–TR3

I

FPU registers:

— STn

— FCS

— FSW

— Tag Word

— FP instruction pointer

— FP opcode

— Operand pointer

Note:

You can save the FPU state by using an FSAVE

or FNSAVE instruction.

For all SMI requests except for power down suspend/

resume, these registers do not have to be saved be-

cause their contents will not change. During a power

down suspend/resume, however, a resume reset clears

these registers back to their default values. In this case,

the suspend SMI handler should read these registers

directly to save them and restore them during the power

up resume. Anytime the SMI handler changes these

registers in the CPU, it must also save and restore them.

Table 11. SMRAM State Save Map

Register

Offset*

7FFCh

7FF8h

7FF4h

7FF0h

7FECh

7FE8h

7FE4h

7FE0h

7FDCh

7FD8h

7FD4h

7FD0h

7FCCh

7FC8h

7FC4h

7FC0h

7FBCh

7FB8h

7FB4h

7FB0h

7FACh

7FA8h

7FA7h–7F98h Reserved

7F94h

7F93h–7F8Ch Reserved

7F88h

7F87h–7F08h Reserved

7F04h

7F02h

7F00h

7EFCh

7EF8h

7EF7h–7E00h Reserved

Register

Writable

CRO

CR3

EFLAGS

EIP

EDI

ESI

EBP

ESP

EBX

EDX

ECX

EAX

DR6

DR7

TR*

LDTR*

GS*

FS*

DS*

SS*

CS*

ES*

No

No

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

No

No

No

No

No

No

No

No

No

No

No

No

No

No

No

No

Yes

Yes

Yes

Yes

No

IDT Base

GDT Base

I/O Trap Word

Halt Auto Restart

I/O Trap Restart

SMM Revision Identifier

State Dump Base

Note:

*Upper 2 bytes are not modified.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 2075 | data delay devices |

| 208-501-21-38 | LED TELEFONSOCKEL T6.8 12V ROT |

| 208-521-21-38 | LED TELEFONSOCKEL T6.8 12V GELB |

| 208-532-21-38 | LED TELEFONSOCKEL T6.8 12V GRUEN |

| 208-930-21-38 | LED TELEFONSOCKEL T6.8 12V BLAU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 207360-1 | 功能描述:管腳和插座連接器 3P PLUG HOUSING RoHS:否 制造商:Molex 系列:1561 產(chǎn)品類型:Contacts 觸點(diǎn)類型:Socket (Female) 節(jié)距: 位置/觸點(diǎn)數(shù)量: 排數(shù): 安裝風(fēng)格:Wire 端接類型:Crimp 外殼材料: 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Tin 電壓額定值: 電流額定值: |

| 20-7360-10 | 功能描述:IC 與器件插座 ELEVATOR STRIP LINE 20 PINS RoHS:否 制造商:Molex 產(chǎn)品:LGA Sockets 節(jié)距:1.02 mm 排數(shù): 位置/觸點(diǎn)數(shù)量:2011 觸點(diǎn)電鍍:Gold 安裝風(fēng)格:SMD/SMT 端接類型:Solder 插座/封裝類型:LGA 2011 工作溫度范圍:- 40 C to + 100 C |

| 207363-000 | 制造商:TE Connectivity 功能描述:MTC50-YH2-004 |

| 207365-1 | 功能描述:管腳和插座連接器 PIN HDR ASSY METRIMATE 3P RoHS:否 制造商:Molex 系列:1561 產(chǎn)品類型:Contacts 觸點(diǎn)類型:Socket (Female) 節(jié)距: 位置/觸點(diǎn)數(shù)量: 排數(shù): 安裝風(fēng)格:Wire 端接類型:Crimp 外殼材料: 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Tin 電壓額定值: 電流額定值: |

| 207365-3 | 功能描述:管腳和插座連接器 PIN HEADER 3P RoHS:否 制造商:Molex 系列:1561 產(chǎn)品類型:Contacts 觸點(diǎn)類型:Socket (Female) 節(jié)距: 位置/觸點(diǎn)數(shù)量: 排數(shù): 安裝風(fēng)格:Wire 端接類型:Crimp 外殼材料: 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Tin 電壓額定值: 電流額定值: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。