- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369945 > P8XC591 (NXP Semiconductors N.V.) HiRel FPGA, Low-Power 1.0?? CMOS Technology PDF資料下載

參數(shù)資料

| 型號: | P8XC591 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | HiRel FPGA, Low-Power 1.0?? CMOS Technology |

| 中文描述: | 單芯片8 - CAN控制器位微控制器 |

| 文件頁數(shù): | 147/160頁 |

| 文件大小: | 601K |

| 代理商: | P8XC591 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁當(dāng)前第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁

2000 Jul 26

147

Philips Semiconductors

Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller

P8xC591

Note

1.

Parts a guaranteed to operate down to 0 Hz.

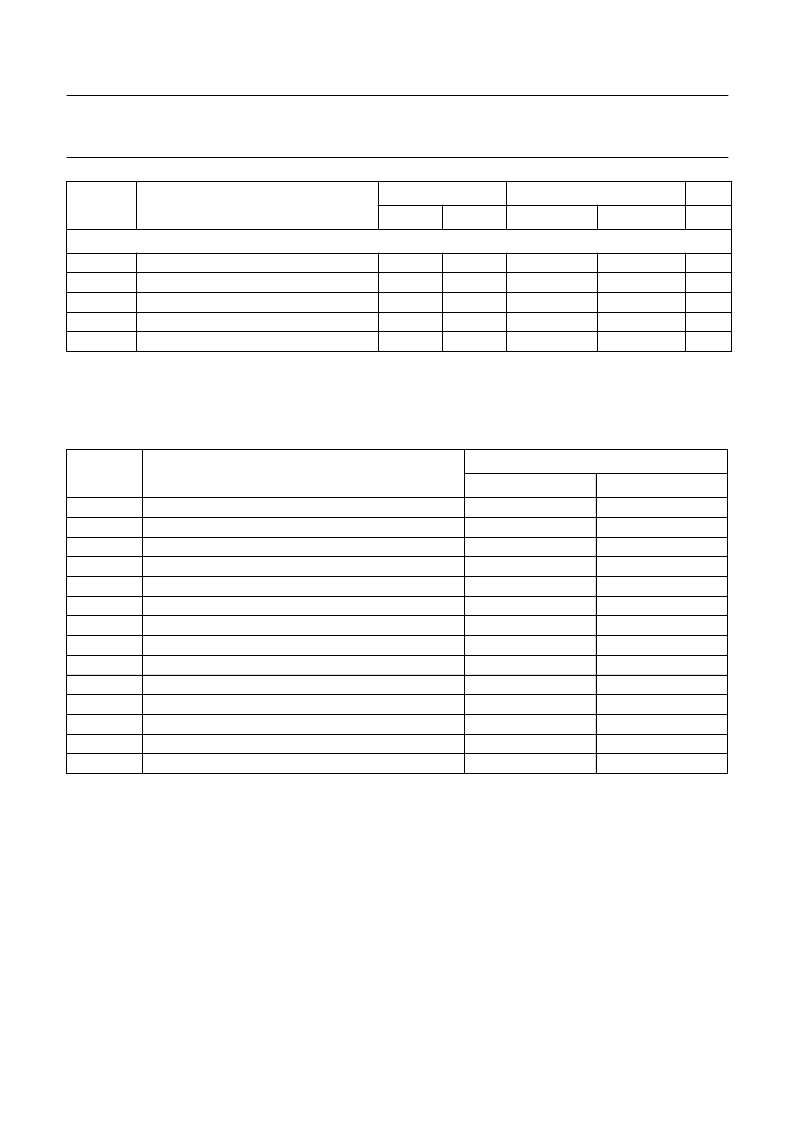

Table 112

I

2

C-bus interface timing

All values referred to V

IH(min)

and V

IL(max)

levels; see Fig.61.

Notes

1.

2.

3.

At 100 kbit/s. At other bit rates this value is inversely proportional to the bit-rate of 100 kbit/s.

Determined by the external bus-line capacitance and the external bus-line pull-resistor, this must be < 1

μ

s.

Spikes on the SDA and SCL lines with a duration of less than 3 t

CLK

will be filtered out. Maximum capacitance on

bus-lines SDA and SCL = 400 pF.

t

CLK

= 1/f

CLK

= one oscillator clock period at pin XTAL1. For 83 ns < t

CLK

< 285 ns (12 MHz > f

CLK

> 3.5 MHz) the

SI01 interface meets the I

2

C-bus specification for bit-rates up to 100 kbit/s.

These values are guaranteed but not 100% production tested.

4.

5.

UART Timing - Shift Register Mode;

see Fig.59

t

XLXL

t

QVXH

t

XHQX

t

XHDX

t

XHDV

serial port clock cycle time

output data setup to clock rising edge

output data hold after clock rising edge

input data hold after clock rising edge

clock rising edge to input data valid

500

284

53

0

6 t

CLK

ns

ns

ns

ns

ns

5 t

CLK

133

t

CLK

30

0

284

5 t

CLK

133

SYMBOL

PARAMETER

I

2

C-BUS

INPUT

≥

7 t

CLK

≥

8 t

CLK

≥

7 t

CLK

≤

1

μ

s

≤

0.3

μ

s

≥

250 ns

≥

250 ns

≥

250 ns

≥

0 ns

≥

7 t

CLK

≥

7 t

CLK

≥

7 t

CLK

≤

1

μ

s

≤

0.3

μ

s

OUTPUT

> 4.0

μ

s

(1)

> 4.7

μ

s

(1)

> 4.0

μ

s

(1)

(2)

< 3.0

μ

s

(3)

> 10 t

CLK

t

RD

> 1

μ

s

(1)

> 4 t

CLK

> 4 t

CLK

t

FC

> 4.7

μ

s

(1)

> 4.0

μ

s

(1)

> 4.7

μ

s

(1)

(2)

< 0.3

μ

s

(3)

t

HD;STA

t

LOW

t

HIGH

t

RC

t

FC

t

SU;DAT1

t

SU;DAT2

t

SU;DAT3

t

HD;DAT

t

SU;STA

t

SU;STO

t

BUF

t

RD

t

FD

START condition hold time

LOW period of the SCL clock

HIGH period of the SCL clock

rise time of SCL signals

fall time of SCL signals

data set-up time

SDA set-up time (before repeated START condition)

SDA set-up time (before STOP condition)

data hold time

set-up time for a repeated START condition

set-up time for STOP condition

bus free time between

rise time of SDA signals

fall time of SDA signals

SYMBOL

PARAMETER

12 MHz CLOCK

VARIABLE CLOCK

UNIT

MIN.

MAX.

MIN.

MAX.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P90CE201 | 16-bit microcontroller |

| P90CE201AEB | 16-bit microcontroller |

| P9217 | PbS photoconductive detector |

| P930 | CdS photoconductive cell |

| PA025XSB | This technical specification applies to 2.5inch color TFT-LCD panel. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P8XC592 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with on-chip CAN |

| P8XCE598 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with on-chip CAN |

| P8XCL580HFH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low voltage 8-bit microcontrollers with UART, I2C-bus and ADC |

| P8XCL580HFT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low voltage 8-bit microcontrollers with UART, I2C-bus and ADC |

| P8Z77 DELUXE | 制造商:Asus 功能描述:P8Z77-V Deluxe ATX Motherboard |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。