- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1977 > XRT79L71IB-F (Exar Corporation)IC LIU/FRAMER DS3/E3 1CH 208BGA PDF資料下載

參數(shù)資料

| 型號(hào): | XRT79L71IB-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 593/609頁 |

| 文件大小: | 0K |

| 描述: | IC LIU/FRAMER DS3/E3 1CH 208BGA |

| 標(biāo)準(zhǔn)包裝: | 126 |

| 控制器類型: | DS3/E3 調(diào)幀器 |

| 接口: | LIU |

| 電源電壓: | 3.15 V ~ 3.45 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 208-LBGA |

| 供應(yīng)商設(shè)備封裝: | 208-STBGA(17x17) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁第273頁第274頁第275頁第276頁第277頁第278頁第279頁第280頁第281頁第282頁第283頁第284頁第285頁第286頁第287頁第288頁第289頁第290頁第291頁第292頁第293頁第294頁第295頁第296頁第297頁第298頁第299頁第300頁第301頁第302頁第303頁第304頁第305頁第306頁第307頁第308頁第309頁第310頁第311頁第312頁第313頁第314頁第315頁第316頁第317頁第318頁第319頁第320頁第321頁第322頁第323頁第324頁第325頁第326頁第327頁第328頁第329頁第330頁第331頁第332頁第333頁第334頁第335頁第336頁第337頁第338頁第339頁第340頁第341頁第342頁第343頁第344頁第345頁第346頁第347頁第348頁第349頁第350頁第351頁第352頁第353頁第354頁第355頁第356頁第357頁第358頁第359頁第360頁第361頁第362頁第363頁第364頁第365頁第366頁第367頁第368頁第369頁第370頁第371頁第372頁第373頁第374頁第375頁第376頁第377頁第378頁第379頁第380頁第381頁第382頁第383頁第384頁第385頁第386頁第387頁第388頁第389頁第390頁第391頁第392頁第393頁第394頁第395頁第396頁第397頁第398頁第399頁第400頁第401頁第402頁第403頁第404頁第405頁第406頁第407頁第408頁第409頁第410頁第411頁第412頁第413頁第414頁第415頁第416頁第417頁第418頁第419頁第420頁第421頁第422頁第423頁第424頁第425頁第426頁第427頁第428頁第429頁第430頁第431頁第432頁第433頁第434頁第435頁第436頁第437頁第438頁第439頁第440頁第441頁第442頁第443頁第444頁第445頁第446頁第447頁第448頁第449頁第450頁第451頁第452頁第453頁第454頁第455頁第456頁第457頁第458頁第459頁第460頁第461頁第462頁第463頁第464頁第465頁第466頁第467頁第468頁第469頁第470頁第471頁第472頁第473頁第474頁第475頁第476頁第477頁第478頁第479頁第480頁第481頁第482頁第483頁第484頁第485頁第486頁第487頁第488頁第489頁第490頁第491頁第492頁第493頁第494頁第495頁第496頁第497頁第498頁第499頁第500頁第501頁第502頁第503頁第504頁第505頁第506頁第507頁第508頁第509頁第510頁第511頁第512頁第513頁第514頁第515頁第516頁第517頁第518頁第519頁第520頁第521頁第522頁第523頁第524頁第525頁第526頁第527頁第528頁第529頁第530頁第531頁第532頁第533頁第534頁第535頁第536頁第537頁第538頁第539頁第540頁第541頁第542頁第543頁第544頁第545頁第546頁第547頁第548頁第549頁第550頁第551頁第552頁第553頁第554頁第555頁第556頁第557頁第558頁第559頁第560頁第561頁第562頁第563頁第564頁第565頁第566頁第567頁第568頁第569頁第570頁第571頁第572頁第573頁第574頁第575頁第576頁第577頁第578頁第579頁第580頁第581頁第582頁第583頁第584頁第585頁第586頁第587頁第588頁第589頁第590頁第591頁第592頁當(dāng)前第593頁第594頁第595頁第596頁第597頁第598頁第599頁第600頁第601頁第602頁第603頁第604頁第605頁第606頁第607頁第608頁第609頁

XRT79L71

PRELIMINARY

69

1-CHANNEL DS3/E3 CLEAR-CHANNEL FRAMERLIU COMBO - CC/HDLC ARCHITECTURE

REV. P2.0.0

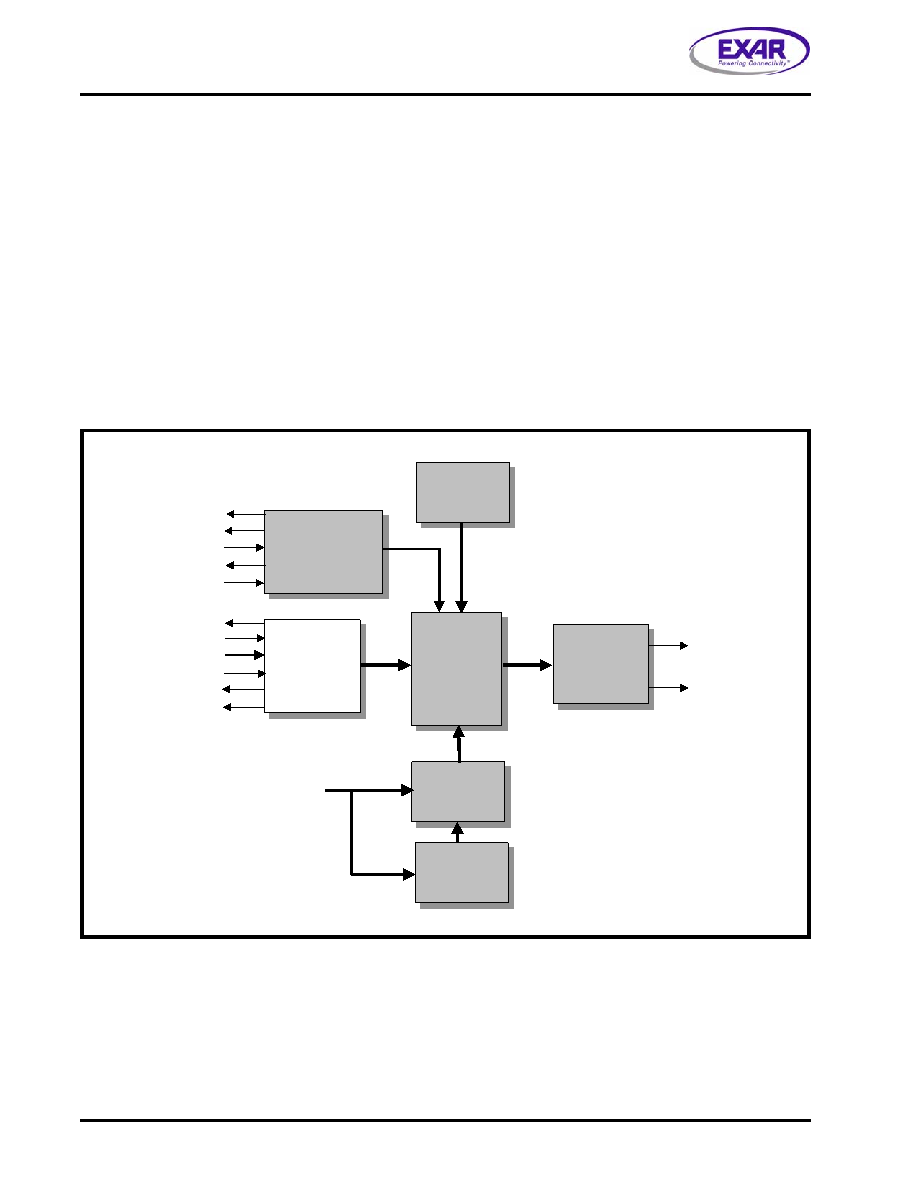

The Transmit Overhead Data Input Interface block

The Transmit LAPD Controller block

The Transmit FEAC Controller block

The Transmit DS3 Framer block

The Transmit DS3 LIU Interface block

4.2.1

TRANSMIT PAYLOAD DATA INPUT INTERFACE BLOCK

The Transmit Payload Data Input Interface block is the very first functional block within the Transmit Direction

of the XRT79L71 that we will discuss for Clear-Channel Framer Applications.

Figure 29 presents an

illustration of the Transmit Direction circuitry whenever the XRT79L71 has been configured to operate in the

DS3 Clear-Channel Framer Mode, with the Transmit Payload Data Input Interface block highlighted.

The purpose of the Transmit Payload Data Input Interface block is to accept payload data from some system-

side or up-stream source and to pass this payload data along to the Transmit DS3 Framer block that will

ultimately map this payload data into the payload bits within each outbound DS3 frame.

In order to accomplish this, the Transmit Payload Data Input Interface block has numerous input and output

pins. Table 13 presents a list and a brief definition of each of these pins.

FIGURE 29. ILLUSTRATION OF THE FUNCTIONAL BLOCK DIAGRAM OF THE TRANSMIT DIRECTION CIRCUITRY, WHEN

THE

XRT79L71 HAS BEEN CONFIGURED TO OPERATE IN THE DS3 CLEAR-CHANNEL FRAMER MODE (WITH THE

TRANSMIT PAYLOAD DATA INPUT INTERFACE BLOCK HIGHLIGHTED

Transmit

Payload Data

Input

Interface

Block

Transmit

Payload Data

Input

Interface

Block

Transmit

DS3/E3

Framer

Block

Transmit

DS3/E3

Framer

Block

Tranmit

DS3/E3

LIU Block

Tranmit

DS3/E3

LIU Block

TxSer

TxNib[3:0]

TxInClk

TRING

TTIP

Transmit

Overhead Data

Input Interface

Block

Transmit

Overhead Data

Input Interface

Block

TxOHClk

TxOHIns

TxOHInd

TxOH

TxOHEnable

TxOHFrame

TxNibClk

TxFrame

Tx LAPD

Controller

Block

Tx LAPD

Controller

Block

From Microprocessor

Interface Block

Tx LAPD

Buffer

(90 Bytes)

Tx LAPD

Buffer

(90 Bytes)

Tx FEAC

Processor

Block

Tx FEAC

Processor

Block

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT81L27IV-F | IC LIU EI 7CH 3.3V 128TQFP |

| XRT82D20IW-F | IC LIU E1 SGL 28SOJ |

| XRT82L24AIV-F | IC LIU E1 QAUD 100TQFP |

| XRT83D10IW | IC LIU T1/E1 SGL 28SOJ |

| XRT83L30IV-F | IC LIU LH/SH T1/E1 SGL 64TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT79L72 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L72IB | 制造商:EXAR 制造商全稱:EXAR 功能描述:2 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L73 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L73IB | 制造商:EXAR 制造商全稱:EXAR 功能描述:3 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L74 | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。