- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > intel386 DX (Intel Corp.) 32-Bit CHMOS Microprocessor With Integrated Memory Management(32位CHMOS 微處理器帶集成存儲(chǔ)管理) PDF資料下載

參數(shù)資料

| 型號: | intel386 DX |

| 廠商: | Intel Corp. |

| 英文描述: | 32-Bit CHMOS Microprocessor With Integrated Memory Management(32位CHMOS 微處理器帶集成存儲(chǔ)管理) |

| 中文描述: | 32位CHMOS微處理器集成內(nèi)存管理(32位CHMOS微處理器帶集成存儲(chǔ)管理) |

| 文件頁數(shù): | 109/139頁 |

| 文件大小: | 1587K |

| 代理商: | INTEL386 DX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁當(dāng)前第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁

Intel386

TM

DX MICROPROCESSOR

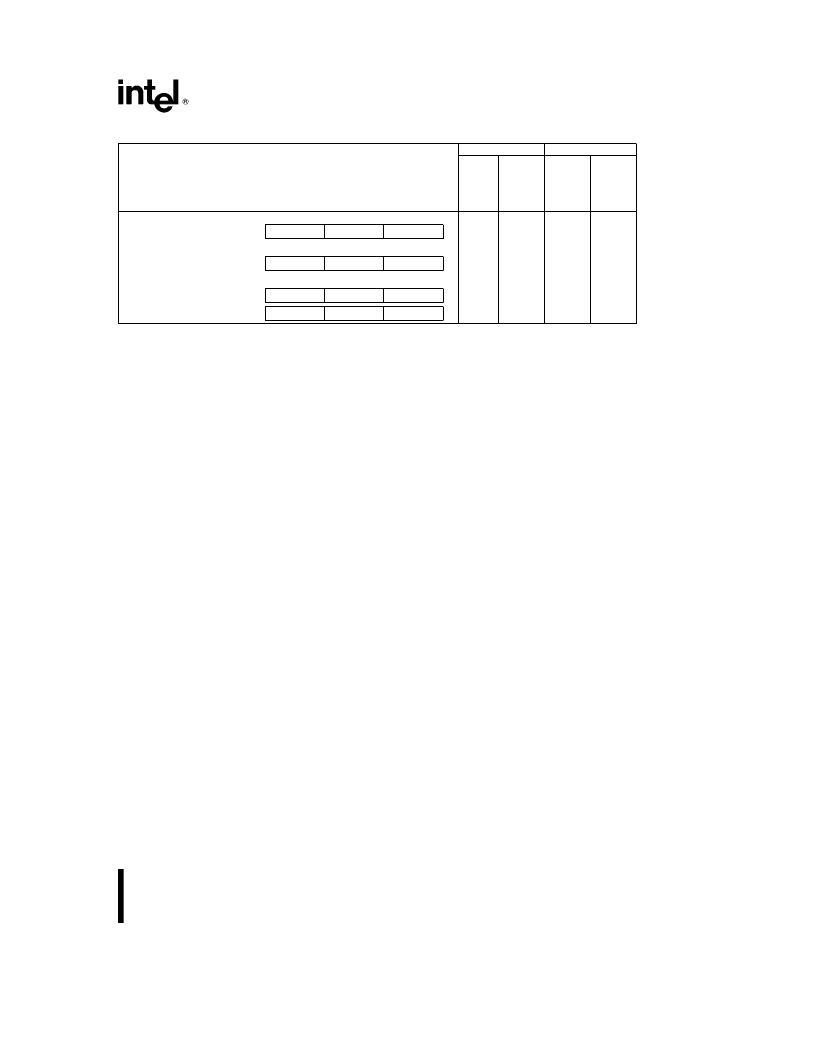

Table 6-1. Intel386

TM

DX Instruction Set Clock Count Summary

(Continued)

CLOCK COUNT

NOTES

Real

Address

Mode or

Virtual

8086

Mode

Real

Address

Mode or

Virtual

8086

Mode

INSTRUCTION

FORMAT

Protected

Virtual

Address

Mode

Protected

Virtual

Address

Mode

SMSW

e

Store Machine

Status Word

0 0 0 0 1 1 1 1

0 0 0 0 0 0 0 1

mod 1 0 0

r/m

2/2

2/2

b, c

h, l

STR

e

Store Task Register

To Register/Memory

0 0 0 0 1 1 1 1

0 0 0 0 0 0 0 0

mod 0 0 1

r/m

N/A

2/2

a

h

VERR

e

Verify Read Accesss

Register/Memory

0 0 0 0 1 1 1 1

0 0 0 0 0 0 0 0

mod 1 0 0

r/m

N/A

10/11

a

g, h, j, p

VERW

e

Verify Write Accesss

0 0 0 0 1 1 1 1

0 0 0 0 0 0 0 0

mod 1 0 1

r/m

N/A

15/16

a

g, h, j, p

INSTRUCTION NOTES FOR TABLE 6-1

Notes a through c apply to Intel386 DX Real Address Mode only:

a. This is a Protected Mode instruction. Attempted execution in Real Mode will result in exception 6 (invalid opcode).

b. Exception 13 fault (general protection) will occur in Real Mode if an operand reference is made that partially or fully

extends beyond the maximum CS, DS, ES, FS or GS limit, FFFFH. Exception 12 fault (stack segment limit violation or not

present) will occur in Real Mode if an operand reference is made that partially or fully extends beyond the maximum SS limit.

c. This instruction may be executed in Real Mode. In Real Mode, its purpose is primarily to initialize the CPU for Protected

Mode.

Notes d through g apply to Intel386 DX Real Address Mode and Intel386 DX Protected Virtual Address Mode:

d. The Intel386 DX uses an early-out multiply algorithm. The actual number of clocks depends on the position of the most

significant bit in the operand (multiplier).

Clock counts given are minimum to maximum. To calculate actual clocks use the following formula:

Actual Clock

e

if m

k l

0 then max (

[

log

2

l

m

l

]

, 3)

a

b clocks:

if m

e

0 then 3

a

b clocks

In this formula, m is the multiplier, and

b

e

9 for register to register,

b

e

12 for memory to register,

b

e

10 for register with immediate to register,

b

e

11 for memory with immediate to register.

e. An exception may occur, depending on the value of the operand.

f. LOCK

Y

is automatically asserted, regardless of the presence or absence of the LOCK

Y

prefix.

g. LOCK

Y

is asserted during descriptor table accesses.

Notes h through r apply to Intel386 DX Protected Virtual Address Mode only:

h. Exception 13 fault (general protection violation) will occur if the memory operand in CS, DS, ES, FS or GS cannot be used

due to either a segment limit violation or access rights violation. If a stack limit is violated, an exception 12 (stack segment

limit violation or not present) occurs.

i. For segment load operations, the CPL, RPL, and DPL must agree with the privilege rules to avoid an exception 13 fault

(general protection violation). The segment’s descriptor must indicate ‘‘present’’ or exception 11 (CS, DS, ES, FS, GS not

present). If the SS register is loaded and a stack segment not present is detected, an exception 12 (stack segment limit

violation or not present) occurs.

j. All segment descriptor accesses in the GDT or LDT made by this instruction will automatically assert LOCK

Y

to maintain

descriptor integrity in multiprocessor systems.

k. JMP, CALL, INT, RET and IRET instructions referring to another code segment will cause an exception 13 (general

protection violation) if an applicable privilege rule is violated.

l. An exception 13 fault occurs if CPL is greater than 0 (0 is the most privileged level).

m. An exception 13 fault occurs if CPL is greater than IOPL.

n. The IF bit of the flag register is not updated if CPL is greater than IOPL. The IOPL and VM fields of the flag register are

updated only if CPL

e

0.

o. The PE bit of the MSW (CR0) cannot be reset by this instruction. Use MOV into CR0 if desiring to reset the PE bit.

p. Any violation of privilege rules as applied to the selector operand does not cause a protection exception; rather, the zero

flag is cleared.

q. If the coprocessor’s memory operand violates a segment limit or segment access rights, an exception 13 fault (general

protection exception) will occur before the ESC instruction is executed. An exception 12 fault (stack segment limit violation

or not present) will occur if the stack limit is violated by the operand’s starting address.

r. The destination of a JMP, CALL, INT, RET or IRET must be in the defined limit of a code segment or an exception 13 fault

(general protection violation) will occur.

109

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Intel386 EX | Highly Integrated, 32-Bit, Fully Static Embedded Micropocessor(32位高集成完全靜態(tài)嵌入式微處理器) |

| INTEL386 SXSA | 5-V 32-Bit Fully Static Embedded Microprocessor(5V,32位完全靜態(tài)嵌入式微處理器) |

| intel386 SX | 32-Bit CPU With a 16-Bit External Data Bus And a 24-bit External Address Bus(帶16位內(nèi)部數(shù)據(jù)總線和24位內(nèi)部地址總線32位微處理器) |

| INTEL386 | Intel386 EX Embedded Microprocessor |

| Intel387 dx | DX Math Coprocessor(32位數(shù)學(xué)協(xié)處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL386SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:MICROPROCESSOR |

| INTEL387 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM SX MATH COPROCESSOR |

| INTEL387DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Intel387 DX - MATH COPROCESSOR |

| INTEL387SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387 SX - MATH COPROCESSOR |

| INTEL387TMDX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM DX MATH COPROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。