- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > intel386 DX (Intel Corp.) 32-Bit CHMOS Microprocessor With Integrated Memory Management(32位CHMOS 微處理器帶集成存儲管理) PDF資料下載

參數(shù)資料

| 型號: | intel386 DX |

| 廠商: | Intel Corp. |

| 英文描述: | 32-Bit CHMOS Microprocessor With Integrated Memory Management(32位CHMOS 微處理器帶集成存儲管理) |

| 中文描述: | 32位CHMOS微處理器集成內(nèi)存管理(32位CHMOS微處理器帶集成存儲管理) |

| 文件頁數(shù): | 82/139頁 |

| 文件大?。?/td> | 1587K |

| 代理商: | INTEL386 DX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁當前第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁

Intel386

TM

DX MICROPROCESSOR

231630–21

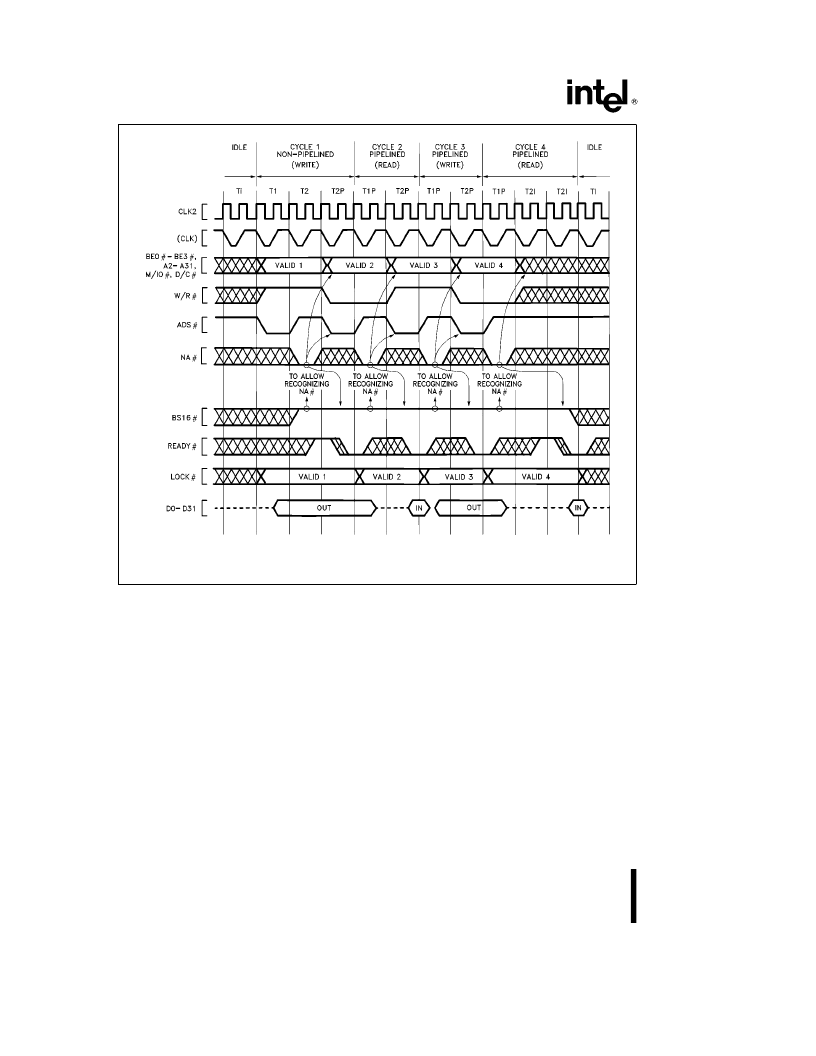

Following any idle bus state (Ti) the address is always non-pipelined and NA

Y

is only sampled during wait states. To start address pipelining

after an idle state requires a non-pipelined cycle with at least one wait state (cycle 1 above).

The pipelined cycles (2, 3, 4 above) are shown with various numbers of wait states.

Figure 5-17. Fastest Transition to Pipelined Address Following Idle Bus State

2) The next address may appear as early as the bus

state after NA

Y

was sampled asserted (see Fig-

ures 5-16 or 5-17). In that case, state T2P is en-

tered immediately. However, when there is not an

internal bus request already pending, the next ad-

dress will not be available immediately after NA

Y

is asserted and T2I is entered instead of T2P (see

Figure 5-19 Cycle 3). Provided the current bus cy-

cle isn’t yet acknowledged by READY

Y

asserted,

T2P will be entered as soon as the Intel386 DX

does drive the next address. External hardware

should therefore observe the ADS

Y

output as

confirmation the next address is actually being

driven on the bus.

3) Once NA

Y

is sampled asserted, the Intel386 DX

commits itself to the highest priority bus request

that is pending internally. It can no longer perform

another 16-bit transfer to the same address should

BS16

Y

be asserted externally, so thereafter

must assume the current bus size is 32 bits.

Therefore if NA

Y

is sampled asserted within a

bus cycle, BS16

Y

must be negated thereafter in

that bus cycle (see Figures 5-16, 5-17, 5-19).

Consequently, do not assert NA

Y

during bus cy-

cles which must have BS16

Y

driven asserted.

See

5.4.3.6 Dynamic Bus Sizing with Pipelined

Address.

4) Any address which is validated by a pulse on the

Intel386 DX ADS

Y

output will remain stable on

the address pins for at least two processor clock

periods. The Intel386 DX cannot produce a new

address more frequently than every two proces-

sor clock periods (see Figures 5-16, 5-17, 5-19).

5) Only the address and bus cycle definition of the

very next bus cycle is available. The pipelining ca-

pability cannot look further than one bus cycle

ahead (see Figure 5-19 Cycle 1).

82

相關PDF資料 |

PDF描述 |

|---|---|

| Intel386 EX | Highly Integrated, 32-Bit, Fully Static Embedded Micropocessor(32位高集成完全靜態(tài)嵌入式微處理器) |

| INTEL386 SXSA | 5-V 32-Bit Fully Static Embedded Microprocessor(5V,32位完全靜態(tài)嵌入式微處理器) |

| intel386 SX | 32-Bit CPU With a 16-Bit External Data Bus And a 24-bit External Address Bus(帶16位內(nèi)部數(shù)據(jù)總線和24位內(nèi)部地址總線32位微處理器) |

| INTEL386 | Intel386 EX Embedded Microprocessor |

| Intel387 dx | DX Math Coprocessor(32位數(shù)學協(xié)處理器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL386SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:MICROPROCESSOR |

| INTEL387 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM SX MATH COPROCESSOR |

| INTEL387DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Intel387 DX - MATH COPROCESSOR |

| INTEL387SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387 SX - MATH COPROCESSOR |

| INTEL387TMDX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM DX MATH COPROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。