- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > intel386 DX (Intel Corp.) 32-Bit CHMOS Microprocessor With Integrated Memory Management(32位CHMOS 微處理器帶集成存儲管理) PDF資料下載

參數(shù)資料

| 型號: | intel386 DX |

| 廠商: | Intel Corp. |

| 英文描述: | 32-Bit CHMOS Microprocessor With Integrated Memory Management(32位CHMOS 微處理器帶集成存儲管理) |

| 中文描述: | 32位CHMOS微處理器集成內(nèi)存管理(32位CHMOS微處理器帶集成存儲管理) |

| 文件頁數(shù): | 25/139頁 |

| 文件大?。?/td> | 1587K |

| 代理商: | INTEL386 DX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁

Intel386

TM

DX MICROPROCESSOR

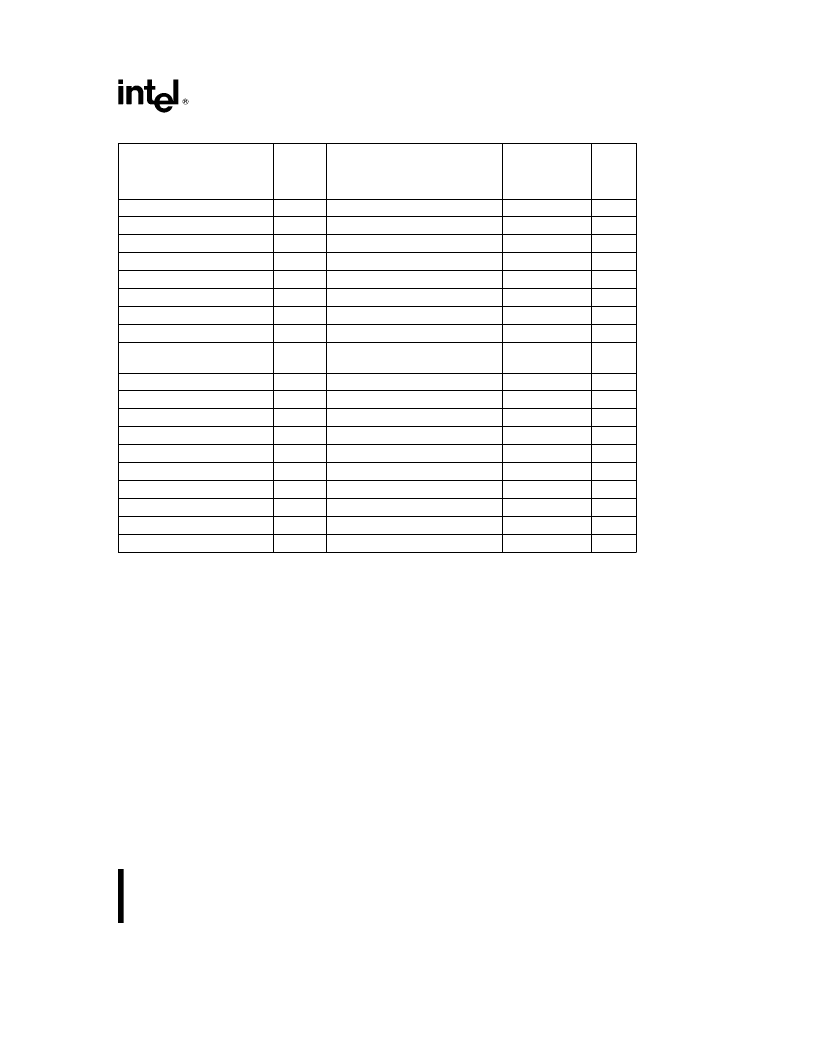

Table 2-5. Interrupt Vector Assignments

Instruction Which

Can Cause

Exception

Return Address

Points to

Faulting

Instruction

Function

Interrupt

Number

Type

Divide Error

0

DIV, IDIV

YES

FAULT

TRAP

*

Debug Exception

1

any instruction

YES

NMI Interrupt

2

INT 2 or NMI

NO

NMI

One Byte Interrupt

3

INT

NO

TRAP

Interrupt on Overflow

4

INTO

NO

TRAP

Array Bounds Check

5

BOUND

YES

FAULT

Invalid OP-Code

6

Any Illegal Instruction

YES

FAULT

Device Not Available

7

ESC, WAIT

YES

FAULT

Double Fault

8

Any Instruction That Can

Generate an Exception

ABORT

Coprocessor Segment Overrun

9

ESC

NO

ABORT

Invalid TSS

10

JMP, CALL, IRET, INT

YES

FAULT

Segment Not Present

11

Segment Register Instructions

YES

FAULT

Stack Fault

12

Stack References

YES

FAULT

General Protection Fault

13

Any Memory Reference

YES

FAULT

Intel Reserved

15

Page Fault

14

Any Memory Access or Code Fetch

YES

FAULT

Coprocessor Error

16

ESC, WAIT

YES

FAULT

Intel Reserved

17–31

Two Byte Interrupt

0–255

INT n

NO

TRAP

*

Some debug exceptions may report both traps on the previous instruction, and faults on the next instruction.

string moves). When an interrupt occurs the proces-

sor reads an 8-bit vector supplied by the hardware

which identifies the source of the interrupt, (one of

224 user defined interrupts). The exact nature of the

interrupt sequence is discussed in section 5.

The IF bit in the EFLAG registers is reset when an

interrupt is being serviced. This effectively disables

servicing additional interrupts during an interrupt

service routine. However, the IF may be set explicitly

by the interrupt handler, to allow the nesting of inter-

rupts. When an IRET instruction is executed the

original state of the IF is restored.

2.9.4 Non-Maskable Interrupt

Non-maskable interrupts provide a method of servic-

ing very high priority interrupts. A common example

of the use of a non-maskable interrupt (NMI) would

be to activate a power failure routine. When the NMI

input is pulled high it causes an interrupt with an

internally supplied vector value of 2. Unlike a normal

hardware interrupt, no interrupt acknowledgment se-

quence is performed for an NMI.

While executing the NMI servicing procedure, the In-

tel386 DX will not service further NMI requests, until

an interrupt return (IRET) instruction is executed or

the processor is reset. If NMI occurs while currently

servicing an NMI, its presence will be saved for serv-

icing after executing the first IRET instruction. The IF

bit is cleared at the beginning of an NMI interrupt to

inhibit further INTR interrupts.

2.9.5 Software Interrupts

A third type of interrupt/exception for the Intel386

DX is the software interrupt. An INT n instruction

causes the processor to execute the interrupt serv-

ice routine pointed to by the nth vector in the inter-

rupt table.

25

相關PDF資料 |

PDF描述 |

|---|---|

| Intel386 EX | Highly Integrated, 32-Bit, Fully Static Embedded Micropocessor(32位高集成完全靜態(tài)嵌入式微處理器) |

| INTEL386 SXSA | 5-V 32-Bit Fully Static Embedded Microprocessor(5V,32位完全靜態(tài)嵌入式微處理器) |

| intel386 SX | 32-Bit CPU With a 16-Bit External Data Bus And a 24-bit External Address Bus(帶16位內(nèi)部數(shù)據(jù)總線和24位內(nèi)部地址總線32位微處理器) |

| INTEL386 | Intel386 EX Embedded Microprocessor |

| Intel387 dx | DX Math Coprocessor(32位數(shù)學協(xié)處理器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL386SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:MICROPROCESSOR |

| INTEL387 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM SX MATH COPROCESSOR |

| INTEL387DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Intel387 DX - MATH COPROCESSOR |

| INTEL387SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387 SX - MATH COPROCESSOR |

| INTEL387TMDX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM DX MATH COPROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。