- 您現(xiàn)在的位置:買賣IC網 > PDF目錄224505 > MT29F4G08BABWP 512M X 8 FLASH 2.7V PROM, 18 ns, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | MT29F4G08BABWP |

| 元件分類: | PROM |

| 英文描述: | 512M X 8 FLASH 2.7V PROM, 18 ns, PDSO48 |

| 封裝: | LEAD FREE, TSOP1-48 |

| 文件頁數(shù): | 28/57頁 |

| 文件大小: | 1057K |

| 代理商: | MT29F4G08BABWP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

PDF: 09005aef818a56a7 / Source: 09005aef81590bdd

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2gb_nand_m29b__2.fm - Rev. I 1/06 EN

34

2004 Micron Technology, Inc. All rights reserved.

2, 4, 8Gb: x8/x16 Multiplexed NAND Flash Memory

Command Definitions

RESET Operation

RESET FFh

The RESET command is used to put the memory device into a known condition and to

abort a command sequence in progress.

RANDOM READ, PROGRAM, and ERASE commands can be aborted while the device is

in the busy state. The contents of the memory location being programmed or the block

being erased are no longer valid. The data may be partially erased or programmed, and

is invalid. The command register is cleared and is ready for the next command.

The status register contains the value E0h when WP# is HIGH; otherwise it is written

with a 60h value. R/B# goes low for tRST after the RESET command is written to the

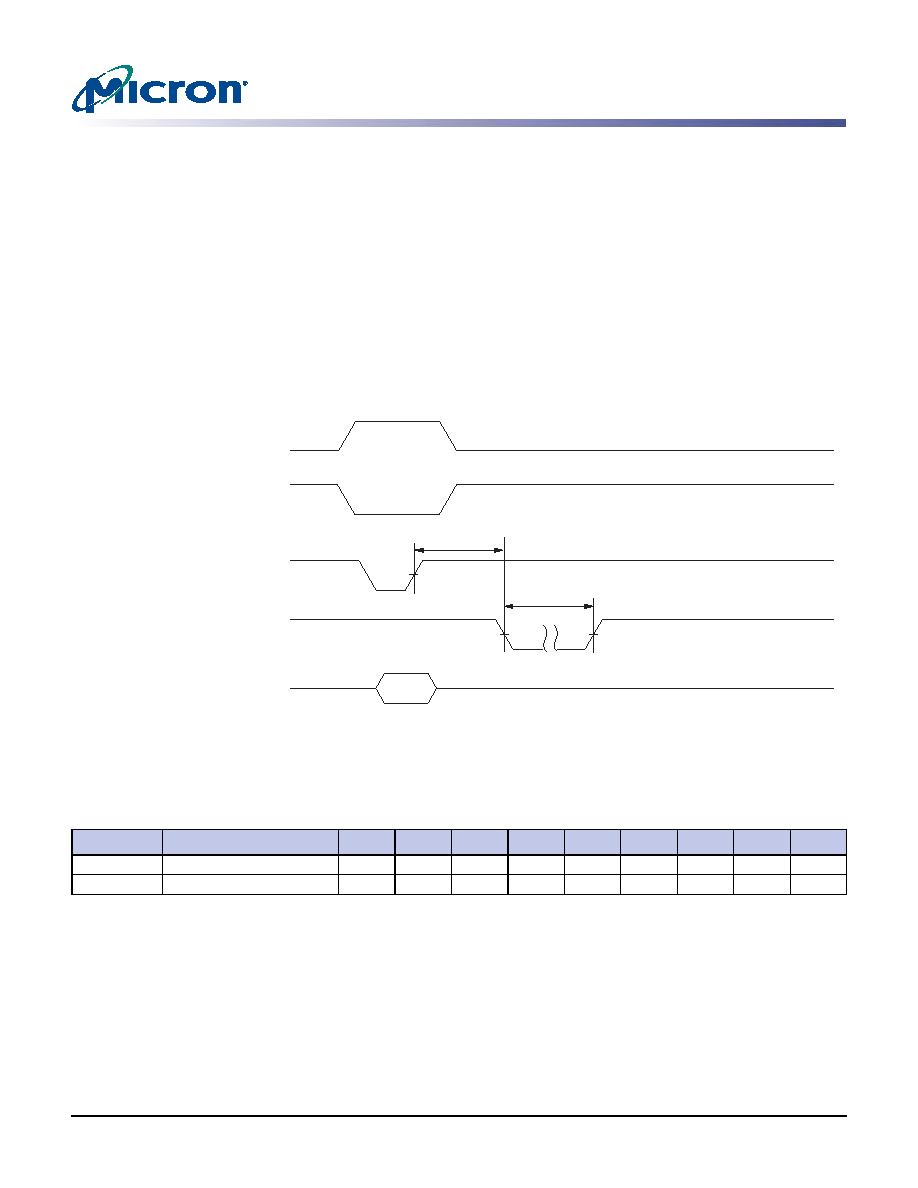

Figure 29:

RESET Operation

Table 10:

Status Register Contents After RESET Operation

Condition

Status

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Hex

WP# HIGH

Ready

1

000

00

E0h

WP# LOW

Ready and write protected

0

1

000

00

60h

CLE

CE#

WE#

R/B#

I/Ox

tRST

tWB

FF

RESET

Command

相關PDF資料 |

PDF描述 |

|---|---|

| MT36JSZF51272PDY-1G6XX | 512M X 72 DDR DRAM MODULE, DMA240 |

| MT3S04AU | UHF BAND, Si, NPN, RF SMALL SIGNAL TRANSISTOR |

| MT41J512M4JE-187EIT:A | 64M X 4 DDR DRAM, PBGA82 |

| MT42C8255RG-7TR | 256K X 8 VIDEO DRAM, 70 ns, PDSO40 |

| MT46V32M16TG-75ELIT | 32M X 16 DDR DRAM, 0.75 ns, PDSO66 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT29F4G08BABWP-ET | 功能描述:IC FLASH 4GBIT 48TSOP RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:1 系列:- 格式 - 存儲器:RAM 存儲器類型:SDRAM 存儲容量:256M(8Mx32) 速度:143MHz 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應商設備封裝:90-VFBGA(8x13) 包裝:托盤 其它名稱:Q2841869 |

| MT29F4G08BABWP-ET TR | 功能描述:IC FLASH 4GBIT 48TSOP RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:1 系列:- 格式 - 存儲器:RAM 存儲器類型:SDRAM 存儲容量:256M(8Mx32) 速度:143MHz 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應商設備封裝:90-VFBGA(8x13) 包裝:托盤 其它名稱:Q2841869 |

| MT29F4G08BBBWP | 功能描述:IC FLASH 4GBIT 48TSOP RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:1 系列:- 格式 - 存儲器:RAM 存儲器類型:SDRAM 存儲容量:256M(8Mx32) 速度:143MHz 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應商設備封裝:90-VFBGA(8x13) 包裝:托盤 其它名稱:Q2841869 |

發(fā)布緊急采購,3分鐘左右您將得到回復。