- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361246 > QADCRM Queued Analog-to-Digital Converter Reference Manual PDF資料下載

參數(shù)資料

| 型號: | QADCRM |

| 英文描述: | Queued Analog-to-Digital Converter Reference Manual |

| 中文描述: | 排隊(duì)模擬到數(shù)字轉(zhuǎn)換器參考手冊 |

| 文件頁數(shù): | 82/122頁 |

| 文件大?。?/td> | 940K |

| 代理商: | QADCRM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁當(dāng)前第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁

MOTOROLA

8-2

INTERRUPTS

QADC

REFERENCE MANUAL

If interrupts are enabled for an event, the QADC requests interrupt service when the

event occurs. Using interrupts does not require continuously polling the status flags to

see if an event has taken place. However, status flags must be cleared after an inter-

rupt is serviced, in order to disable the interrupt request.

In both polled and interrupt-driven operating modes, status flags must be re-enabled

after an event occurs. Flags are re-enabled by clearing appropriate QASR bits in a par-

ticular sequence. The register must first be read, then zeros must be written to the

flags that are to be cleared. If a new event occurs between the time that the register is

read and the time that it is written, the associated flag is not cleared.

8.3 Interrupt Sources

The QADC includes four sources of interrupt service requests, each of which is sepa-

rately enabled. Each time the result is written for the last conversion command word

(CCW) in a queue, the completion flag for the corresponding queue is set, and when

enabled, an interrupt request is generated. In the same way, each time the result is

written for a CCW with the pause bit set, the queue pause flag is set, and when en-

abled, an interrupt request is generated. Refer to

Table 8-1

.

The pause and complete interrupts for queue 1 and queue 2 have separate interrupt

vector numbers, so that each source can be separately serviced.

8.4 QADC Interrupt Register

QADCINT specifies the priority level of QADC interrupt requests and the vector pro-

vided during an interrupt acknowledge cycle. The interrupt level for queue 1 and queue

2 may be different. The interrupt register is read/write accessible in supervisor data

space only. The implemented interrupt register fields can be read and written, re-

served locations read zero and writes have no effect. They are typically written once

when the software initializes the QADC, and not changed afterwards.

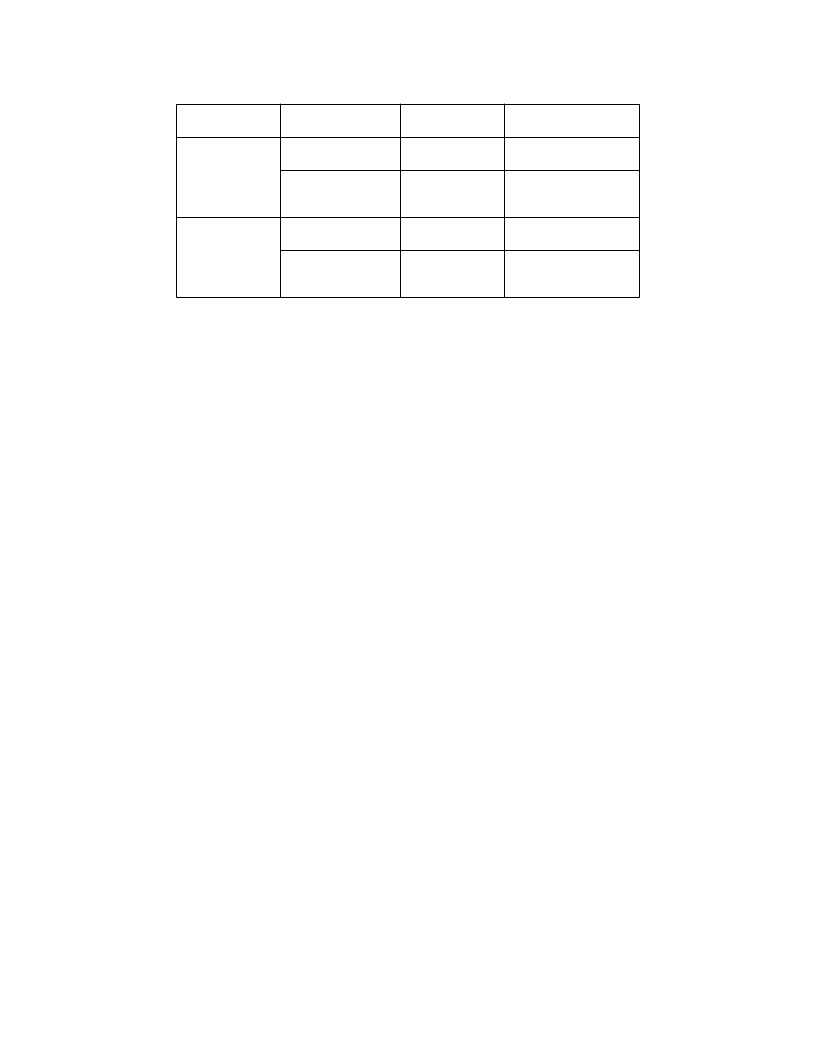

Table 8-1 QADC Status Flags and Interrupt Sources

Queue

Queue

Activity

Status Flag

Interrupt Enable Bit

Queue 1

Result written to last

CCW in Queue 1

Result written for a

CCW with pause bit

set in Queue 1

Result written to last

CCW in Queue 2

Result written for a

CCW with pause bit

set in Queue 2

CF1

CF1

PF1

PF1

Queue 2

CF2

CF2

PF2

PF2

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QAK2E104JCP | PLASTIC FILM CAPACITORS |

| QAK2E104JTP | PLASTIC FILM CAPACITORS |

| QAK2E104KCP | PLASTIC FILM CAPACITORS |

| QAK2E104KTP | PLASTIC FILM CAPACITORS |

| QAK2E105JCP | PLASTIC FILM CAPACITORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QAE100 | 制造商:P-DUKE 制造商全稱:Power Mate Technology Co., LTD 功能描述:QUARTER-BRICK DC-DC CONVERTER 2:1 ULTRA WIDE INPUT RANGE UP TO 108Watts |

| QAE100W | 制造商:P-DUKE 制造商全稱:Power Mate Technology Co., LTD 功能描述:QUARTER-BRICK DC-DC CONVERTER 4:1 ULTRA WIDE INPUT RANGE UP TO 90Watts |

| QAE150 | 制造商:P-DUKE 制造商全稱:Power Mate Technology Co., LTD 功能描述:QUARTER-BRICK DC-DC CONVERTER 2:1 ULTRA WIDE INPUT RANGE UP TO 150Watts |

| QAE150W | 制造商:P-DUKE 制造商全稱:Power Mate Technology Co., LTD 功能描述:QUARTER-BRICK DC-DC CONVERTER 4:1 ULTRA WIDE INPUT RANGE UP TO 132Watts |

| QAEP | 制造商:Omnimount 功能描述:10.6 ~ 21 Inch Adjustable 1.5 Inch NPT Pipe Extension |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。