- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8102A H.100/H.110 Interface and Time-Slot Interchangers PDF資料下載

參數(shù)資料

| 型號: | T8102A |

| 英文描述: | H.100/H.110 Interface and Time-Slot Interchangers |

| 中文描述: | H.100/H.110接口和時隙Interchangers |

| 文件頁數(shù): | 53/112頁 |

| 文件大小: | 1408K |

| 代理商: | T8102A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當(dāng)前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

Lucent Technologies Inc.

49

Advance Data Sheet

November 1999

H.100/H.110 Interfaces and Time-Slot Interchangers

Ambassador T8100A, T8102, and T8105

2 Architecture and Functional Description

(continued)

2.5 Clocking Section

(continued)

2.5.8 Clock Control Register Definitions

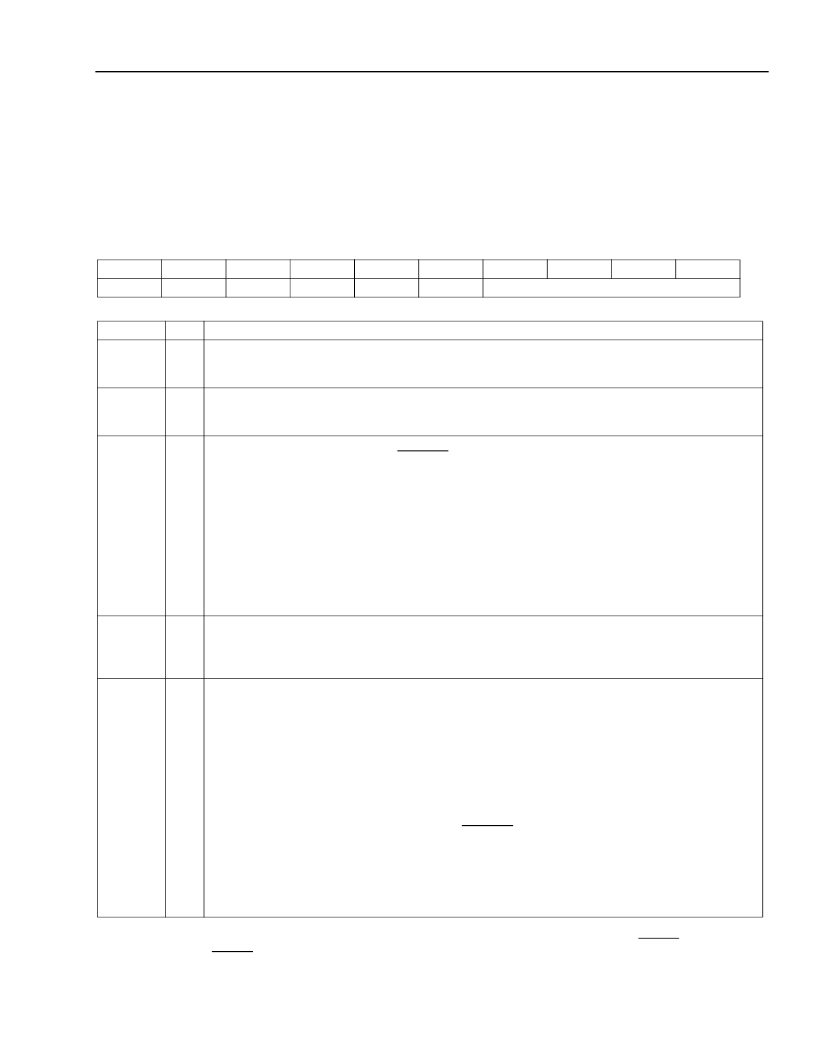

Table 46. CKM: Clocks, Main Clock Selection, 0x00

The first register, 0x00, is the clock main (CKM) register. There are ten registers to control the various aspects of

clocking.

* Selecting A clocks synchronizes the devices to CT_C8A and /CT_FRAMEA; selecting B clocks synchronizes the devices to CT_C8B and

/CT_FRAMEB; MVIPuses /C4, C2, and /FR_COMP; H-MVIPuses /C16+/–, /C4, C2, and /FR_COMP; SC2 uses SCLKX2 and /FR_COMP;

SC4/8 requires SCLK, SCLKX2, and /FR_COMP MC-1 fallback clocks use the same inputs and state machine as the A clocks and B clocks

with an inversion selected from register CKP A pictorial view of the various clocks is shown in Section 4.8.1 Clock Alignment.

Reg

CKM

R/W

—

Bit 7

PAE

Bit 6

PAS

Bit 5

CCD

Bit 4

CKI

Bit 3

Bit 2

Bit 1

Bit 0

CKSEL

Symbol

PAE

Bit

7

Description

Phase Alignment Enable.

PAE = 0,

PAE = 1,

Phase Alignment.

PAS = 0,

PAS = 1,

The CCD bit is the compatibility clock direction. This controls the I/O for the compatibility

clocks /C16+/–, /C4, C2, SCLK, SCLKX2, and /FR_COMP (compatibility frame). The user can

think of the CCD bit (in some respects) as a master/slave select for the compatibility clocks,

though other registers require proper setup to establish true master or slave operation. The

devices will assume control of this bit during a fallback if the previously designated compatibil-

ity clock master fails.

CCD = 0,

Slave, monitors compatibility signals.

CCD = 1,

Master, drives compatibility signals.

Note:

If bit 4 of the programmable clocks register, CKP is low, then the state machines of the

A clock and B clock will assume this is an MC-1 system and interpret the clocks as

/C4(L/R) and FRAME(L/R). If this bit is high, then it interprets the clocks as C8(A/B)

and FRAME(A/B).

CKI is used to invert the output of the clock selector, i.e., the signal which feeds the main

divider, resource divider, and DPLL:

CKI = 0,

Normal.

CKI = 1,

Invert.

3—0 The decode for the clock selector (CKSEL) is illustrated below. These selections determine

which input state machine is utilized*:

CKSEL = 0000,

Internal oscillator.

CKSEL = 0001,

CT_NETREF1 or CT_NETREF2 (CON register bit 5 selects:

if 0 then CT_NETREF1 is selected, if 1 CT_NETREF2).

CKSEL = 0010,

A clocks (C8A & FRAMEA); ECTF or MC-1.

CKSEL = 0011,

B clocks (C8B & FRAMEB); ECTF or MC-1.

CKSEL = 0100,

MVIPis selected, /C4 is selected as the clock reference for PLL #1.

CKSEL = 0101,

H-MVIP s selected, /C16 is selected as the clock reference for

PLL #1.

CKSEL = 0110,

SC-Bus, 2 MHz. SCLKX2 is selected as the clock reference for

PLL #1.

CKSEL = 0111,

SC-Bus, 4 MHz or 8 MHz. SCLK is selected as the clock

reference for PLL #1.

CKSEL = 1000—1111 Selects local references 0—7. When bit 4 of the CON register is set,

these bits select pairs of synchronized inputs.

Retains frequency lock without phase alignment.

Enables phase alignment.

PAS

6

Phase alignment, snap.

Phase alignment, slide.

CCD

5

CKI

4

CKSEL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8105A | H.100/H.110 Interface and Time-Slot Interchangers |

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger |

| T8110 | Version History |

| T8301 | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T810-400B | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HIGH PERFORMANCE TRIACS |

| T8105A | 制造商:AGERE 制造商全稱:AGERE 功能描述:H.100/H.110 Interface and Time-Slot Interchangers |

| T810-600B | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復(fù)通態(tài)電流:120 A 額定重復(fù)關(guān)閉狀態(tài)電壓 VDRM:600 V 關(guān)閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600B | 制造商:STMicroelectronics 功能描述:TRIAC 8A 600V D-PAK |

| T810-600B-TR | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復(fù)通態(tài)電流:120 A 額定重復(fù)關(guān)閉狀態(tài)電壓 VDRM:600 V 關(guān)閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:TO-220AB |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。