- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8102A H.100/H.110 Interface and Time-Slot Interchangers PDF資料下載

參數(shù)資料

| 型號: | T8102A |

| 英文描述: | H.100/H.110 Interface and Time-Slot Interchangers |

| 中文描述: | H.100/H.110接口和時隙Interchangers |

| 文件頁數(shù): | 91/112頁 |

| 文件大?。?/td> | 1408K |

| 代理商: | T8102A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁當(dāng)前第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

Lucent Technologies Inc.

87

Advance Data Sheet

November 1999

H.100/H.110 Interfaces and Time-Slot Interchangers

Ambassador T8100A, T8102, and T8105

4 Electrical Characteristics

(continued)

4.8 H-Bus Timing (Extract from H.100 Spec., Rev. 1.0)

(continued)

4.8.4 ac Electrical Characteristics, Timing, H-Bus (H.100 Spec., Rev. 1.0)

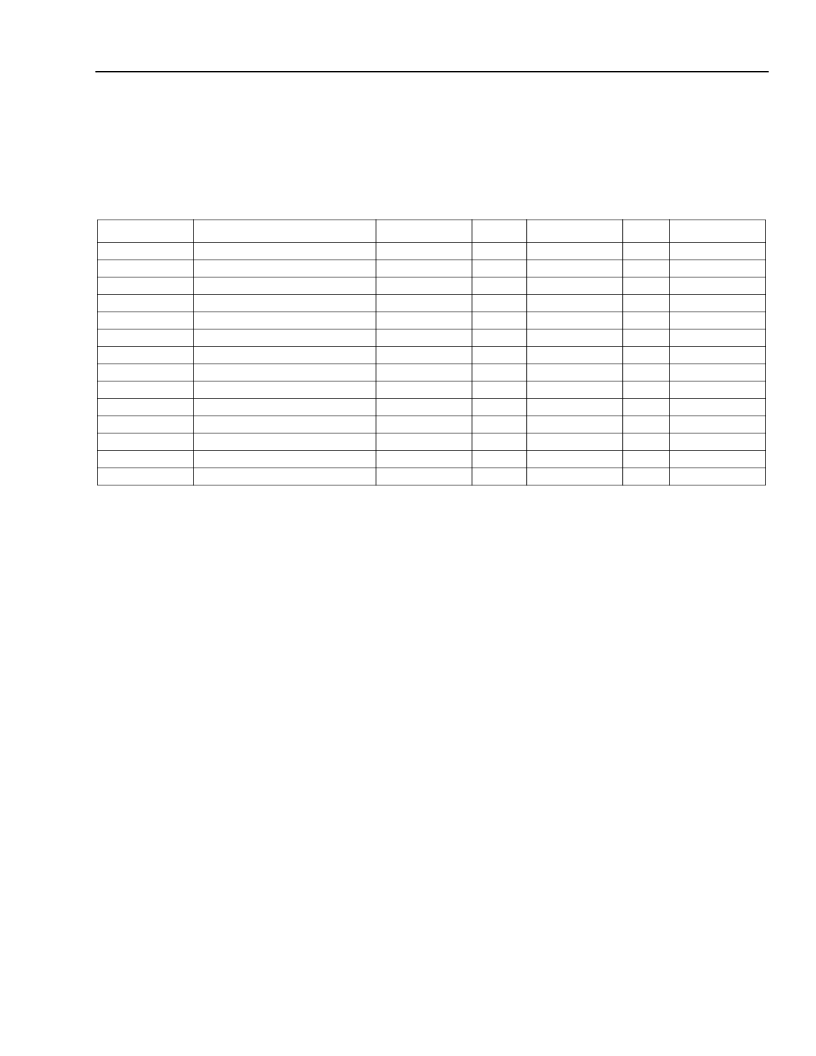

Table 76. ac Electrical Characteristics, Timing, H-Bus (H.100 Spec., Rev. 1.0)

Symbol

—

tC8P

tC8H

tC8L

tSAMP

tDOZ

tZDO

tDOD

tDV

tDIV

tFP

tFS

tFH

Φ

Parameter

Min

0.25

Typ

—

—

—

—

90

—

—

—

—

—

122

—

—

—

Max

2

Unit

V/ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes

1, 2, 4

2, 4, 5

2, 4, 6

2, 4, 6

2, 4, 9

2, 3, 4, 7, 11

2, 3, 4, 7, 11

2, 3, 4, 7

2, 3, 4, 8, 10

2, 4

2, 4

2, 4

2, 4

12

Clock Edge Rate (all clocks)

Clock CT_C8 Period

Clock CT_C8 High Time

Clock CT_C8 Low Time

Data Sample Point

Data Output to HiZ Time

Data HiZ to Output Time

Data Output Delay Time

Data Valid Time

Data Invalid Time

/CT_FRAME Width

/CT_FRAME Setup Time

/CT_FRAME Hold Time

Phase Correction

122.066 –

Φ

49 –

Φ

49 –

Φ

—

–20

0

0

0

102

90

45

45

0

122.074 +

Φ

73 +

Φ

73 +

Φ

—

0

22

22

69

112

180

90

90

10

1. The rise and fall times are determined by the edge rate in V/ns. A maximum edge rate is the fastest rate at which a clock transitions.

CT_NETREF has a separate requirement. (See Section 2.5 Clocking Section.)

2. Measuring conditions, data lines: VTH (threshold voltage) = 1.4 V, VHI (test high voltage) = 2.4 V, VLO (test low voltage) = 0.4 V, input sig-

nal edge rate = 1 V/ns measuring conditions, clock and frame lines: Vt+ (test high voltage) = 2.0 V, Vt– (test low voltage) = 0.6 V, input sig-

nal edge rate = 1 V/ns.

3. Test load—200 pF.

4. When RESET is active, every output driver is 3-stated.

5. tC8P minimum and maximum are under free-run conditions assuming ±32 ppm clock accuracy.

6. Noncumulative, tC8P requirements still need to be met.

7. Measured at the transmitter.

8. Measured at the receiver.

9. For reference only.

10. tDV = maximum clock cable delay + maximum data cable delay + maximum data HiZ to output time = 12 ns + 35 ns + 22 ns = 69 ns. Maxi-

mum clock cable delay and maximum data cable delay are worst-case numbers based on electrical simulation.

11. tDOZ and tZDO apply at every time-slot boundary.

12. F (phase correction) results from PLL timing corrections.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8105A | H.100/H.110 Interface and Time-Slot Interchangers |

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger |

| T8110 | Version History |

| T8301 | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T810-400B | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:HIGH PERFORMANCE TRIACS |

| T8105A | 制造商:AGERE 制造商全稱:AGERE 功能描述:H.100/H.110 Interface and Time-Slot Interchangers |

| T810-600B | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復(fù)通態(tài)電流:120 A 額定重復(fù)關(guān)閉狀態(tài)電壓 VDRM:600 V 關(guān)閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600B | 制造商:STMicroelectronics 功能描述:TRIAC 8A 600V D-PAK |

| T810-600B-TR | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復(fù)通態(tài)電流:120 A 額定重復(fù)關(guān)閉狀態(tài)電壓 VDRM:600 V 關(guān)閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:TO-220AB |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。