- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375989 > FW82371 (Intel Corp.) PCI-TO-ISA / IDE XCELERATOR PIIX4 PDF資料下載

參數(shù)資料

| 型號(hào): | FW82371 |

| 廠商: | Intel Corp. |

| 英文描述: | PCI-TO-ISA / IDE XCELERATOR PIIX4 |

| 中文描述: | PCI到的ISA / IDE的XCELERATOR PIIX4 |

| 文件頁數(shù): | 58/284頁 |

| 文件大小: | 1042K |

| 代理商: | FW82371 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當(dāng)前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁第273頁第274頁第275頁第276頁第277頁第278頁第279頁第280頁第281頁第282頁第283頁第284頁

82371AB (PIIX4)

E

58

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

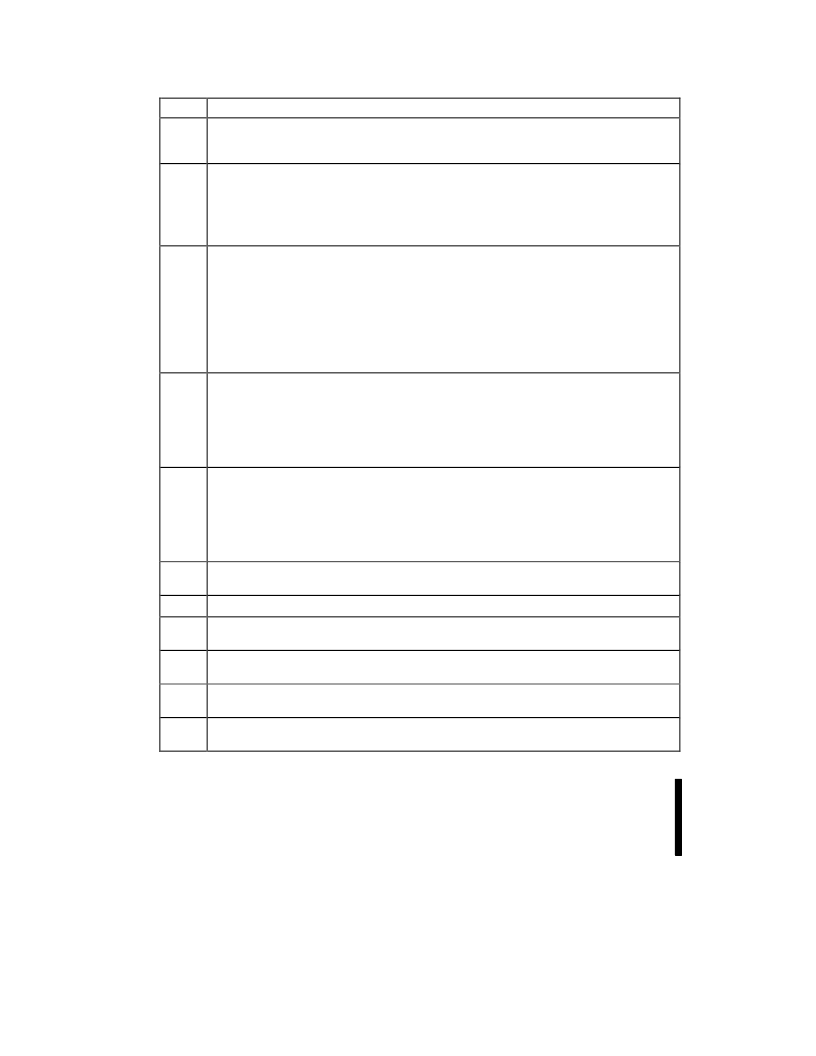

Bit

Description

10

Micro Controller Address Location Enable.

1=Enable MCCS#

and positive PCI decode for

address locations 62h and 66h.

0=Disable MCCS# and positive PCI decode for accesses to these

locations.

9

1-Meg Extended BIOS Enable.

When bit 9=1,

PCI master accesses to locations FFF00000–

FFF7FFFFh are forwarded to ISA and result in the generation of BIOSCS# and XOE#. When

forwarding the additional 512-Kbyte region, PIIX4 allows the PCI address A[23:20] to propagate to

the ISA LA[23:20] lines as all 1’s, aliasing this 512-Kbyte region to the top of the 16-Mbyte space. To

avoid contention, ISA memory must not be present in this region (00F00000–00F7FFFFh). When bit

9=0, PIIX4 does not generate BIOSCS# or XOE# for accesses to this memory region.

8

APIC Chip Select.

When enabled (bit 8=1), APICCS# is asserted for PCI memory accesses to the

programmable I/O APIC region. This cycle is forwarded to the ISA bus. The default I/O APIC

addresses are memory FEC0_0000h and FEC0_0010h. These can be relocated via the APIC Base

Address Relocation Register. When disabled (bit 8=0), the PCI cycle is ignored by PIIX4 and

APICCS# and XOE# are not generated. Note that APICCS# is not generated for ISA-originated

cycles.

This bit is also used to select between GPIO functionality and APIC functionality on APICREQ#,

APICACK#, APICCS#, IRQ0, IRQ8#, and IRQ9OUT# signals. When disabled, these signals become

General Purpose Inputs or Outputs.

7

Extended BIOS Enable.

When bit 7=1 (enabled), PCI master accesses to locations FFF80000–

FFFDFFFFh are forwarded to ISA and result in the generation of BIOSCS# and XOE#. When

forwarding the additional 384-Kbyte region at the top of 4 Gbytes, PIIX4 allows the PCI address

A[23:20] to propagate to the ISA LA[23:20] lines as all 1’s, aliasing this 384-Kbyte region to the top of

the 16-Mbyte space. To avoid contention, ISA memory must not be present in this region

(00F80000–00FDFFFFh). When bit 7=0, PIIX4 does not generate BIOSCS# or XOE# for accesses

to this memory region.

6

Lower BIOS Enable.

When bit 6=1 (enabled), PCI master, or ISA master accesses to the lower 64-

Kbyte BIOS block (E0000–EFFFFh) at the top of 1 Mbyte, or the aliases at the top of 4 Gbyte

(FFFE0000–FFFEFFFFh) result in the generation of BIOSCS# and XOE#. When forwarding the

region at the top of 4 Gbytes to the ISA Bus, the ISA LA[23:20] lines are all 1’s, aliasing this region to

the top of the 16-Mbyte space. To avoid contention, ISA memory must not be present in this region

(00FE0000–00FEFFFFh). When bit 6=0, PIIX4 does not generate BIOSCS# or XOE# during these

accesses and does not forward the accesses to ISA.

5

Coprocessor Error Function Enable.

1=Enable; the FERR# input, when asserted, triggers IRQ13

(internal). FERR# is also used to gate the IGNNE# output. 0=Disable.

4

IRQ12/M Mouse Function Enable.

1=Mouse function; 0=Standard IRQ12 interrupt function.

3

Port 61h Alias Enable.

1=PIIX4 aliases accesses to 63h, 65h, and 67h to 61h. 0=PIIX4 does not

alias 63h, 65h, and 67h to 61h.

2

BIOSCS# Write Protect Enable.

1=Enable (BIOSCS# is asserted for BIOS memory read and write

cycles in decoded BIOS region);

0=Disable (BIOSCS# is only asserted for BIOS read cycles).

1

KBCCS# Enable.

1=Enable KBCS# and XOE# for address locations 60h and 64h. 0=Disable

KBCS#/XOE# for accesses to these locations.

0

RTCCS#/RTCALE Enable.

1=Enable RTCCS#/RTCALE and XOE# for accesses to address

locations 70–77h.

0=Disable RTCCS#/RTCALE and XOE# for these accesses.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FW82801E | Intel 82801E Communications I/O Controller Hub (C-ICH) |

| FWB150 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

| FWB151 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

| FWB1510 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

| FWB152 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FW82371EB | 制造商:Intel 功能描述:IC INTEL 82371EB 352BGA 制造商:Rochester Electronics LLC 功能描述: |

| FW82371EB S L37M | 制造商:Intel 功能描述:Embedded Processor 352-Pin BGA |

| FW82371EB SL37M | 制造商:Intel 功能描述: |

| FW82371MB | 制造商:Rochester Electronics LLC 功能描述:PCI-ISA BRIDGE, T&R, SPEC SL3CG - Bulk |

| FW82439HX | 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。