- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368064 > PM5372-BI Telecommunication IC PDF資料下載

參數(shù)資料

| 型號(hào): | PM5372-BI |

| 英文描述: | Telecommunication IC |

| 中文描述: | 通信集成電路 |

| 文件頁(yè)數(shù): | 38/169頁(yè) |

| 文件大?。?/td> | 989K |

| 代理商: | PM5372-BI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)

TSE Transmission Switch Element Datasheet

Released

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

Document ID: PMC-1991258, Issue 7

38

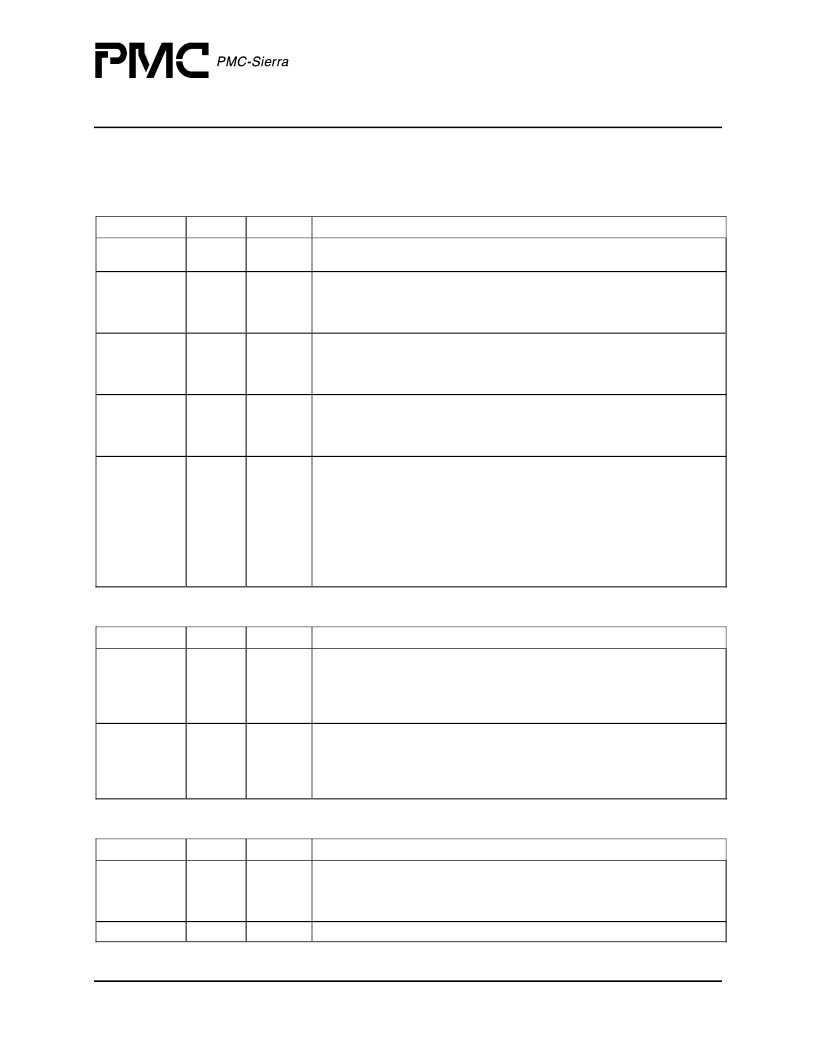

Table 4 Pin Description JTAG Port (5 Signals)

Pin Name

Type

Pin No.

Function

TCK

Input

AR2

Test Clock.

The JTAG test clock signal (TCK) provides timing for test

operations that are carried out using the IEEE P1149.1 test access port.

TMS

Input

AR3

Test Mode Select.

The JTAG test mode select signal (TMS) controls the

test operations that are carried out using the IEEE P1149.1 test access

port. TMS is sampled on the rising edge of TCK. TMS has an integral pull-

up resistor.

TDI

Input

AR1

Test Data Input.

The JTAG test data input signal (TDI) carries test data

into the TSE via the IEEE P1149.1 test access port. TDI is sampled on the

rising edge of TCK. A 30 Kohm external pull-up resistor is recommended

on this pin.

TDO

Tri-state E2

Test Data Output.

The JTAG test data output signal (TDO) carries test

data out of the TSE via the IEEE P1149.1 test access port. TDO is

updated on the falling edge of TCK. TDO is a tri-state output which is

inactive except when scanning of data is in progress.

TRSTB

Input

AV35

Test Reset Bar.

The active low JTAG test reset signal (TRSTB) provides

an asynchronous TSE test access port (TAP) controller reset via the IEEE

P1149.1 test access port. TRSTB is a Schmitt triggered input with an

integral pull-up resistor.

The TAP controller must be placed in the Test-Logic-Reset state after

applying power to the device to guarantee correct device operation. This is

easily accomplished by connecting TRSTB to the RSTB input and

performing a device reset, but is not necessary if another method of

resetting the TAP controller is implemented.

Table 5 Pin Description External Resistors (8 Signals)

Pin Name

Type

Pin No.

Function

RES[4]

RES[3]

RES[2]

RES[1]

Analog

Input

B7

G38

AV33

AN2

Reference Resistor Connection.

An off-chip 3.16k ±1% resistor is

connected between each positive resistor reference pin RES[I] and the

corresponding Kelvin ground contact RESK[I].

RESK[4]

RESK[3]

RESK[2]

RESK[1]

Analog

Input

A7

G39

AW33

AN1

Reference Resistor Connection.

An off-chip 3.16k ±1% resistor is

connected between each positive resistor reference pin RES[I] and the

corresponding Kelvin ground contact RESK[I].

Table 6 Pin Description Analog Test Bus (8 Signals)

Pin Name

Type

Pin No.

Function

ATB0[4]

ATB0[3]

ATB0[2]

ATB0[1]

Analog

D32

AM36

AT8

H4

These pins are used for PMC testing only and should be directly connected

to ground.

ATB1[4]

Analog

D31

These pins are used for PMC testing only and should be directly connected

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM5380 | PMC-2010299 S/UNI-8x155 Telecom Standard Product Data Sheet [1.91 MB] |

| PM554 | Programmable Quad Supply Monitor with Adjustable Reset and Watchdog Timers; Package: SSOP; No of Pins: 16; Temperature Range: -40°C to +85°C |

| PM555 | 1 to 10 watt encapsulated power modules |

| PM556 | Precision Quad Supply Monitor in 6-Lead SOT-23; Package: SOT; No of Pins: 6; Temperature Range: 0°C to +70°C |

| PM560 | Precision Quad Supply Monitor in 6-Lead SOT-23; Package: SOT; No of Pins: 6; Temperature Range: 0°C to +70°C |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM5372BIP | 制造商:PMC-Sierra 功能描述: |

| PM5372-BI-P | 制造商:PMC-Sierra 功能描述: |

| PM5376HFI | 制造商:PMC-Sierra 功能描述: |

| PM5377 | 制造商:PMC 制造商全稱:PMC 功能描述:Single Chip 96-Port STS-1/STM-0 Cross-Connect |

| PM537CE | 制造商:ARTESYN 制造商全稱:Artesyn Technologies 功能描述:Single, dual and triple output 1 to 10.5 Watt AC/DC encapsulated modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。