- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8100A H.100/H.110 Interface and Time-Slot Interchangers PDF資料下載

參數(shù)資料

| 型號: | T8100A |

| 英文描述: | H.100/H.110 Interface and Time-Slot Interchangers |

| 中文描述: | H.100/H.110接口和時隙Interchangers |

| 文件頁數(shù): | 16/112頁 |

| 文件大小: | 1408K |

| 代理商: | T8100A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

12

Lucent Technologies Inc.

Advance Data Sheet

November 1999

H.100/H.110 Interfaces and Time-Slot Interchangers

Ambassador T8100A, T8102, and T8105

1 Product Overview

(continued)

1.4 AmbassadorTSI Architecture

The Ambassadorprogrammable TSIs have been

designed to meet today’s switching requirements. The

T8100A and T8105 TSIs have a hierarchical switching

capability. They can switch between the local input bus

and the local output bus. They also switch between the

H.100/H.110 bus and local bus. The T8102 TSI

switches between the H.100/H.110 bus and the local

bus.

All three TSIs have circuitry for subrate switching and

can interface to other computer telephony standards

such as MVIP SC-Bus, and MC-1*.

1.5 Selecting Between T8105, T8102,

T8100A, and T8100

1.6 Enhanced Local Stream Addressing

Local stream addressing has 1024 locations. Separate

connection and data memories (T8100A, T8105 only)

maintain all necessary information for local stream

interconnections. The streams may operate at maxi-

mum rate on eight physical inputs and eight physical

outputs. Choices for slower input or output rates

allow enabling of additional physical inputs or outputs

for a maximum of 16 pins each. Data rates are

2.048 Mbits/s, 4.096 Mbits/s, or 8.192 Mbits/s.

In addition to the enhanced serial streaming, the local

memories may be used for 8-line-serial-in/1-byte-paral-

lel-out, 1-byte-parallel-in/8-line-serial-out, or 1-byte-

parallel-in/1-byte-parallel-out options. All three data

rates are supported in the parallel modes. The

addresses for the local memories (T8100A, T8105

only) have been simplified so that stream and time-slot

designations are automatically translated to the appro-

priate memory address, regardless of rate or serial/par-

allel modes.

* MC-1 is a multichassis communication standard based on MVIP

The devices support this standard.

1.7 Full H.100 Stream Address Support

The devices provide access to the full 4096 H.100 bus

slots (32 streams x 128 slots) or any standard subset

(H-MVIPhas a maximum 24 streams x 128 time

slots, for example). The number of stored time-slot

addresses is limited to 512 (T8102, T8105 only) at any

one time, but these may be updated on the fly. In addi-

tion, accesses to and from the H.100 bus can be

directed through the 1024 local stream/time slots, giv-

ing a total space of 5120 time slots. Data rates are pro-

grammable on each of the 32 physical streams,

selected in groups of four. The rates are 2.048 Mbits/s,

4.096 Mbits/s, or 8.192 Mbits/s.

1.8 Onboard PLLs and Clock Monitors

The devices use rate multipliers and state machines to

generate onboard frequencies for supporting the

H.100, H-MVIP MVIP MC-1, and SC-Buses. Pins are

provided for coupling the internal clock circuitry with

commonly available clock adapters and jitter attenua-

tors. If external resources are not available, an internal

digital phase-locked loop (DPLL) can be used to gener-

ate all the bus frequencies and remain synchronized to

an 8 kHz reference. One of several clock input refer-

ence sources may be selected, and separate input-

active detection logic can identify the loss of the individ-

ual input references. The entire clocking structure oper-

ates from a 16.384 MHz crystal or external input.

1.9 Phase Alignment of Referenced and

Generated Frames

If this resource is selected, special control logic will cre-

ate bit-sliding in the data streams when the reference

frame and generated frame are out of phase. The bit-

sliding refers to removing a fraction of a bit time per

frame until the frames are in phase.

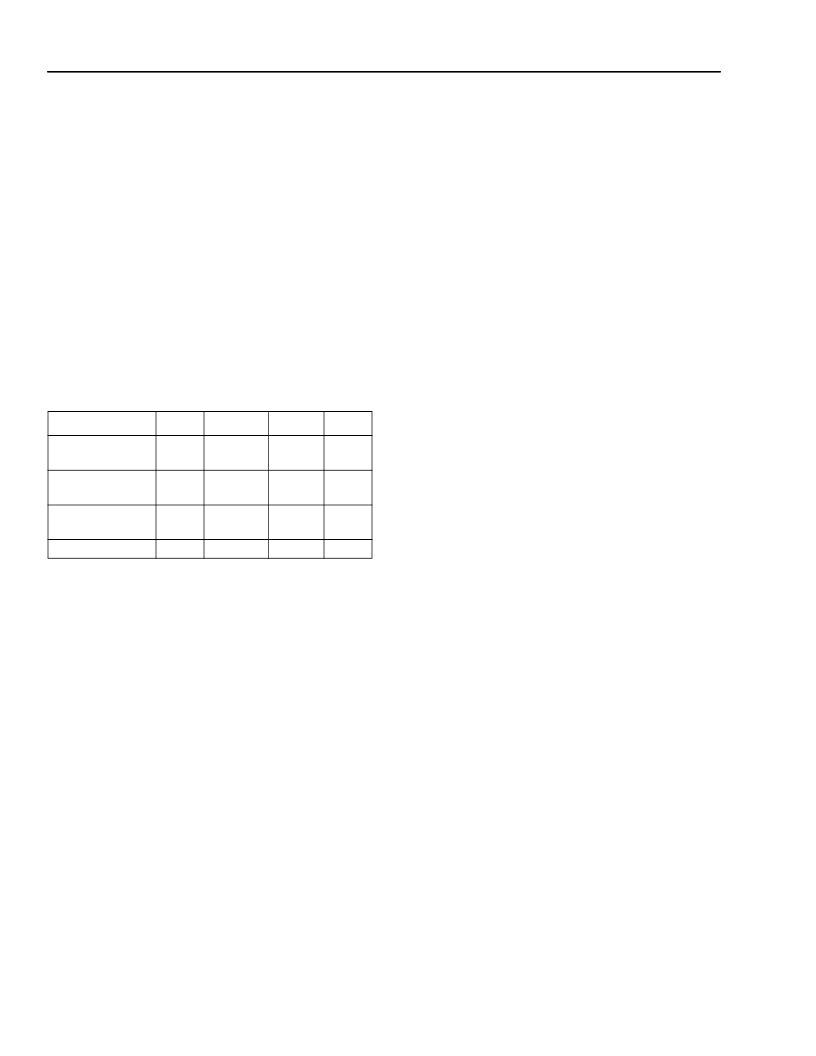

Features

Subrate

switching

Local-to-local

connections

Local-to-H.100

connections

CT_NETREFs

T8100

T8100A

T8102

T8105

—

√

√

√

1,024

1,024

—

1,024

256

256

512

512

1

2

2

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8102A | H.100/H.110 Interface and Time-Slot Interchangers |

| T8105A | H.100/H.110 Interface and Time-Slot Interchangers |

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger |

| T8110 | Version History |

| T8301 | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8100A-BAL | 制造商:Alcatel-Lucent 功能描述:ELECTRONIC COMPONENT |

| T8100A-BAL4DB | 制造商:AGERE 功能描述: |

| T8100-D | 制造商:GE Sensing & Inspection Technologies 功能描述:CO2/TEMP SENS WALL MNT DUAL OUT |

| T8100-E | 制造商:GE Sensing & Inspection Technologies 功能描述:TRANSMITTER, CO2, HUMIDITY, TEMP 制造商:GE MEASUREMENT & CONTROL 功能描述:TRANSMITTER, CO2, HUMIDITY, TEMP; Plug Type:- ;RoHS Compliant: Yes 制造商:GE MEASUREMENT & CONTROL/GE SENSING 功能描述:TRANSMITTER, CO2, HUMIDITY, TEMP; Plug Type:- ;RoHS Compliant: Yes |

| T8100-E-D | 制造商:GE Sensing & Inspection Technologies 功能描述:TRANSMITTER, CO2, HUMIDITY, TEMP 制造商:GE MEASUREMENT & CONTROL 功能描述:TRANSMITTER, CO2, HUMIDITY, TEMP; Plug Type:- ;RoHS Compliant: Yes 制造商:GE MEASUREMENT & CONTROL/GE SENSING 功能描述:TRANSMITTER, CO2, HUMIDITY, TEMP; Plug Type:- ;RoHS Compliant: Yes |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。