- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373200 > KU386 (Intel Corp.) SX MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | KU386 |

| 廠商: | Intel Corp. |

| 英文描述: | SX MICROPROCESSOR |

| 中文描述: | SX微處理器 |

| 文件頁(yè)數(shù): | 17/102頁(yè) |

| 文件大小: | 1268K |

| 代理商: | KU386 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

Intel386

TM

SX MICROPROCESSOR

2.7 Interrupts and Exceptions

Interrupts and exceptions alter the normal program

flow in order to handle external events, report errors

or exceptional conditions. The difference between

interrupts and exceptions is that interrupts are used

to handle asynchronous external events while ex-

ceptions handle instruction faults. Although a pro-

gram can generate a software interrupt via an INT N

instruction, the processor treats software interrupts

as exceptions.

Hardware interrupts occur as the result of an exter-

nal event and are classified into two types: maskable

or non-maskable. Interrupts are serviced after the

execution of the current instruction. After the inter-

rupt handler is finished servicing the interrupt, exe-

cution proceeds with the instruction immediately

after

the interrupted instruction.

Exceptions are classified as faults, traps, or aborts,

depending on the way they are reported and wheth-

er or not restart of the instruction causing the excep-

tion is supported.

Faults

are exceptions that are de-

tected and serviced

before

the execution of the

faulting instruction.

Traps

are exceptions that are

reported immediately

after

the execution of the in-

struction which caused the problem.

Aborts

are ex-

ceptions which do not permit the precise location of

the instruction causing the exception to be deter-

mined.

Thus, when an interrupt service routine has been

completed, execution proceeds from the instruction

immediately following the interrupted instruction. On

the other hand, the return address from an excep-

tion fault routine will always point to the instruction

causing the exception and will include any leading

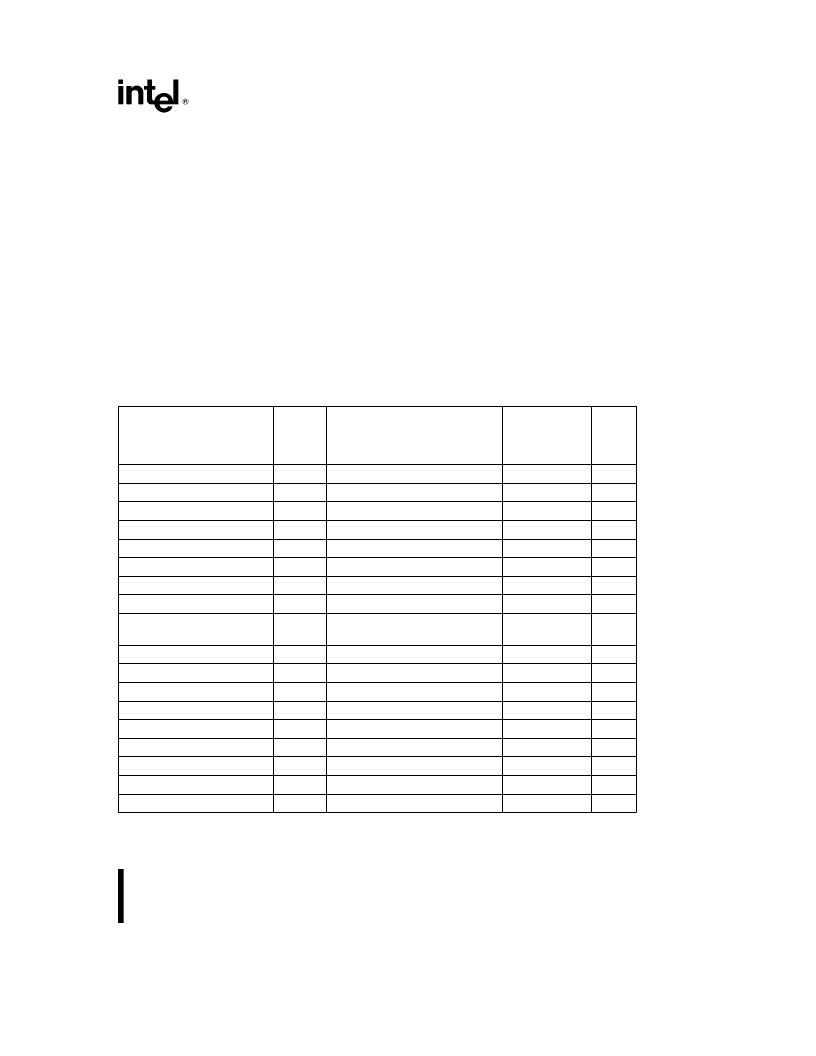

instruction prefixes. Table 2.5 summarizes the possi-

ble interrupts for the Intel386 SX Microprocessor

and shows where the return address points to.

Table 2.5. Interrupt Vector Assignments

Return Address

Points to

Faulting

Instruction

Interrupt

Number

Instruction Which

Can Cause

Exception

Function

Type

Divide Error

0

DIV, IDIV

YES

FAULT

Debug Exception

1

any instruction

YES

TRAP

*

NMI Interrupt

2

INT 2 or NMI

NO

NMI

One Byte Interrupt

3

INT

NO

TRAP

Interrupt on Overflow

4

INTO

NO

TRAP

Array Bounds Check

5

BOUND

YES

FAULT

Invalid OP-Code

6

Any illegal instruction

YES

FAULT

Device Not Available

7

ESC, WAIT

YES

FAULT

Double Fault

8

Any instruction that can

generate an exception

ABORT

Coprocessor Segment Overrun

9

ESC

NO

ABORT

Invalid TSS

10

JMP, CALL, IRET, INT

YES

FAULT

Segment Not Present

11

Segment Register Instructions

YES

FAULT

Stack Fault

12

Stack References

YES

FAULT

General Protection Fault

13

Any Memory Reference

YES

FAULT

Page Fault

14

Any Memory Access or Code Fetch

YES

FAULT

Coprocessor Error

16

ESC, WAIT

YES

FAULT

Intel Reserved

17–32

Two Byte Interrupt

*

Some debug exceptions may report both traps on the previous instruction and faults on the next instruction.

33–255

INT n

NO

TRAP

17

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KU80C186EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC20 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KU-3C-110D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-120A | 制造商:M.E.C. Relays 功能描述: 制造商:Master Electronic Controls (MEC) 功能描述: |

| KU-3C-12A | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-12D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-240A | 制造商:M.E.C. Relays 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。