- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373200 > KU386 (Intel Corp.) SX MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | KU386 |

| 廠商: | Intel Corp. |

| 英文描述: | SX MICROPROCESSOR |

| 中文描述: | SX微處理器 |

| 文件頁數(shù): | 47/102頁 |

| 文件大?。?/td> | 1268K |

| 代理商: | KU386 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當(dāng)前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

Intel386

TM

SX MICROPROCESSOR

when the Intel386 SX Microprocessor issues a new

bus cycle definition and address.

Collectively, the address bus, data bus and all asso-

ciated control signals are referred to simply as ‘the

bus’. When active, the bus performs one of the bus

cycles below:

1. Read from memory space

2. Locked read from memory space

3. Write to memory space

4. Locked write to memory space

5. Read from I/O space (or coprocessor)

6. Write to I/O space (or coprocessor)

7. Interrupt acknowledge (always locked)

8. Indicate halt, or indicate shutdown

Table 5.2 shows the encoding of the bus cycle defi-

nition signals for each bus cycle. See

Bus Cycle

Definition Signals

for additional information.

When the Intel386 SX Microprocessor bus is not

performing one of the activities listed above, it is ei-

ther Idle or in the Hold Acknowledge state, which

may be detected externally. The idle state can be

identified by the Intel386 SX Microprocessor giving

no further assertions on its address strobe output

(ADS

Y

) since the beginning of its most recent bus

cycle, and the most recent bus cycle having been

terminated. The hold acknowledge state is identified

by the Intel386 SX Microprocessor asserting its hold

acknowledge (HLDA) output.

The shortest time unit of bus activity is a bus state. A

bus state is one processor clock period (two CLK2

periods) in duration. A complete data transfer occurs

during a bus cycle, composed of two or more bus

states.

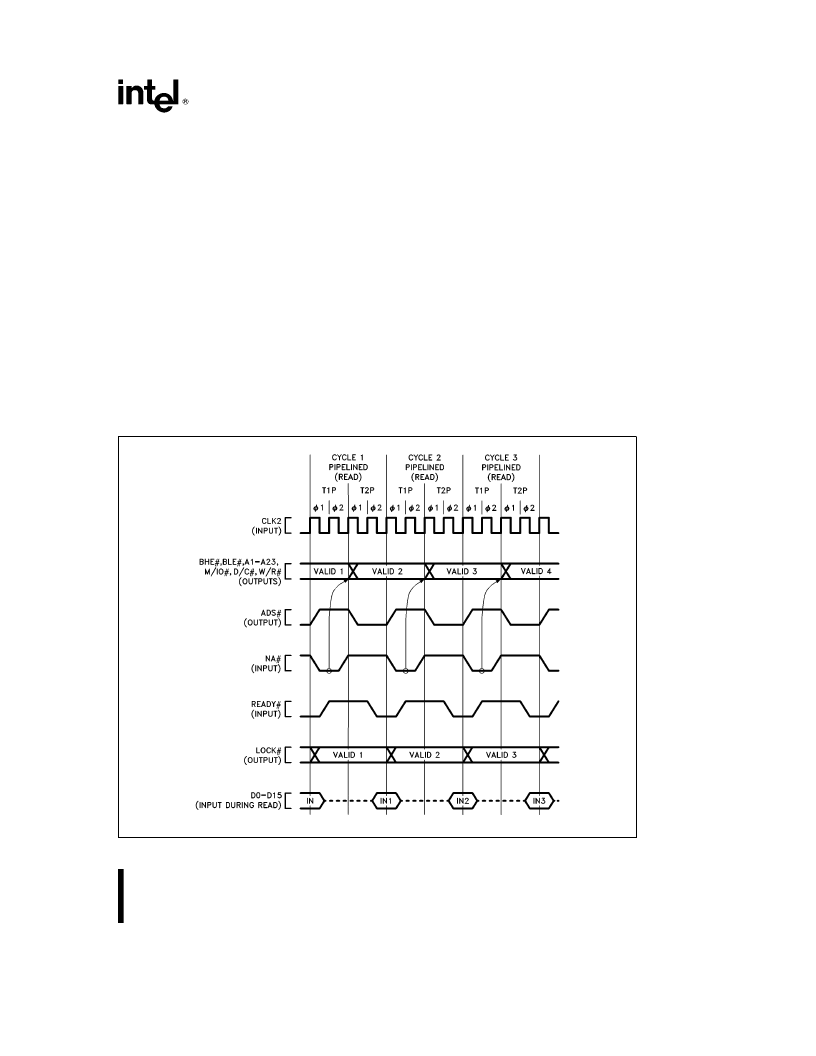

The fastest Intel386 SX Microprocessor bus cycle

requires only two bus states. For example, three

consecutive bus read cycles, each consisting of two

bus states, are shown by Figure 5.4. The bus states

in each cycle are named T1 and T2. Any memory or

I/O address may be accessed by such a two-state

bus cycle, if the external hardware is fast enough.

240187–20

Fastest pipelined bus cycles consist of T1P and T2P

Figure 5.5. Fastest Read Cycles with Pipelined Address Timing

47

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KU80C186EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC20 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KU-3C-110D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-120A | 制造商:M.E.C. Relays 功能描述: 制造商:Master Electronic Controls (MEC) 功能描述: |

| KU-3C-12A | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-12D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-240A | 制造商:M.E.C. Relays 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。