- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373200 > KU386 (Intel Corp.) SX MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | KU386 |

| 廠商: | Intel Corp. |

| 英文描述: | SX MICROPROCESSOR |

| 中文描述: | SX微處理器 |

| 文件頁數(shù): | 70/102頁 |

| 文件大小: | 1268K |

| 代理商: | KU386 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當(dāng)前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

Intel386

TM

SX MICROPROCESSOR

Functional operating range: V

CC

e

5V

g

10%; T

CASE

e

0

§

C to 100

§

C

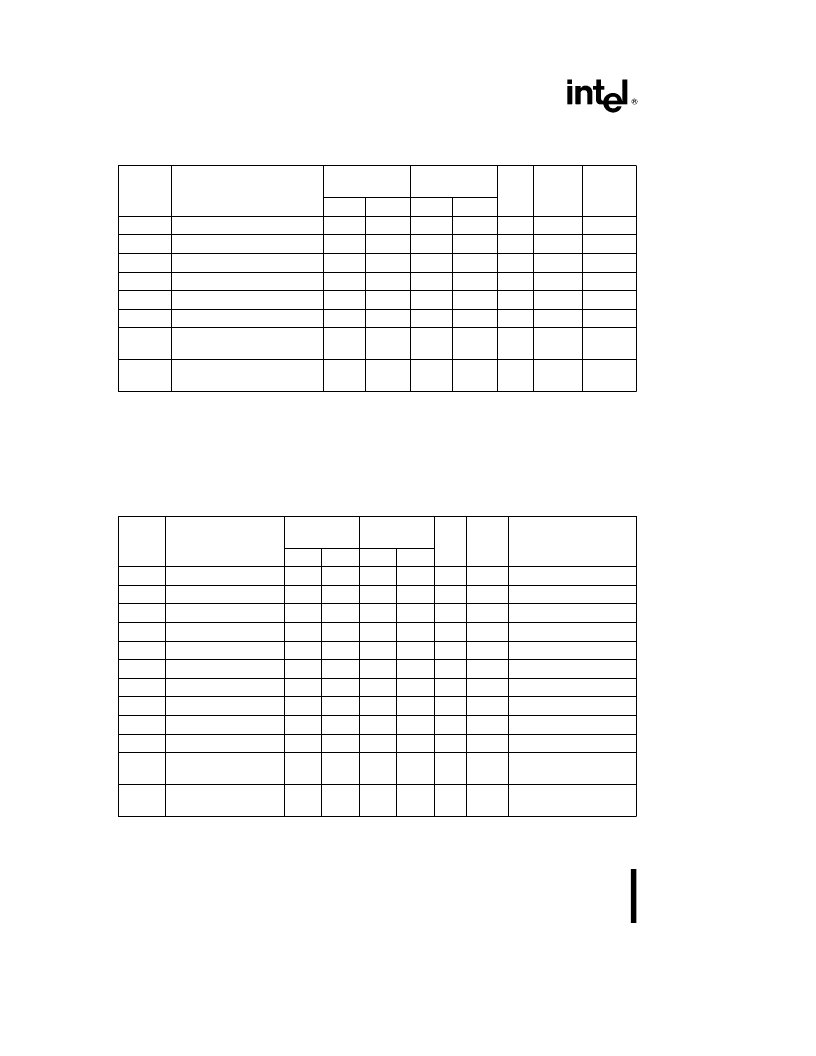

Table 7.5. Intel386

TM

SX Microprocessor A.C. CharacteristicsD33 MHz and 25 MHz

(Continued)

Symbol

Parameter

33 MHz

Intel386 SX

25 MHz

Intel386 SX

Unit

Figure

Notes

Min

Max

Min

Max

t

23

HOLD Setup Time

9

9

ns

7.4

t

24

HOLD Hold Time

2

3

ns

7.4

t

25

RESET Setup Time

5

8

ns

7.7

t

26

RESET Hold Time

2

3

ns

7.7

t

27

NMI, INTR Setup Time

5

6

ns

7.4

(Note 2)

t

28

NMI, INTR Hold Time

5

6

ns

7.4

(Note 2)

t

29

PEREQ, ERROR

Y

, BUSY

Y

,

FLT

Y

Setup Time

5

6

ns

7.4

(Note 2)

t

30

PEREQ, ERROR

Y

, BUSY

Y

,

FLT

Y

Hold Time

4

5

ns

7.4

(Note 2)

NOTES:

1. Float condition occurs when maximum output current becomes less than I

LO

in magnitude. Float delay is not 100%

tested.

2. These inputs are allowed to be asynchronous to CLK2. The setup and hold specifications are given for testing purposes

to assure recognition within a specific CLK2 period.

3. These are not tested. They are guaranteed by design characterization.

4. Tested with CL set at 50 pF. See Figures 7 and 8 for load capacitance derating curve.

5. Minimum time not 100% tested.

Table 7.6. Low Power (LP) Intel386

TM

SX Microprocessor A.C. CharacteristicsD33 MHz and 25 MHz

Symbol

Parameter

33 MHz

Intel386 SX

25 MHz

Intel386 SX

Unit

Figure

Notes

Min

Max

Min

Max

Operating Frequency

2

33

2

25

MHz

Half CLK2 Frequency

t

1

CLK2 Period

15

250

20

250

ns

7.3

t

2a

CLK2 HIGH Time

6.25

7

ns

7.3

at 2V

(3)

t

2b

CLK2 HIGH Time

4.0

4

ns

7.3

at (V

CC

b

0.8)V

(3)

; Note 3

t

3a

CLK2 LOW Time

6.25

7

ns

7.3

at 2V

(3)

t

3b

CLK2 LOW Time

4.5

5

ns

7.3

at 0.8V

(3)

t

4

CLK2 Fall Time

4

7

ns

7.3

(V

CC

b

0.8)V to 0.8V

(3)

0.8V to (V

CC

b

0.8)V

(3)

C

L

e

50 pF

(4)

t

5

CLK2 Rise Time

4

7

ns

7.3

t

6

A

23

–A

1

Valid Delay

4

15

4

17

ns

7.5

t

7

A

23

–A

1

Float Delay

BHE

Y

, BLE

Y

, LOCK

Y

Valid Delay

4

20

4

30

ns

7.6

(Note 1)

t

8

4

15

4

17

ns

7.5

C

L

e

50 pF

(4)

t

9

BHE

Y

, BLE

Y

, LOCK

Y

Float Delay

4

20

4

30

ns

7.6

(Note 1)

70

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KU80C186EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC20 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KU-3C-110D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-120A | 制造商:M.E.C. Relays 功能描述: 制造商:Master Electronic Controls (MEC) 功能描述: |

| KU-3C-12A | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-12D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-240A | 制造商:M.E.C. Relays 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。