- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373200 > KU386 (Intel Corp.) SX MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | KU386 |

| 廠商: | Intel Corp. |

| 英文描述: | SX MICROPROCESSOR |

| 中文描述: | SX微處理器 |

| 文件頁數(shù): | 92/102頁 |

| 文件大小: | 1268K |

| 代理商: | KU386 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁當(dāng)前第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

Intel386

TM

SX MICROPROCESSOR

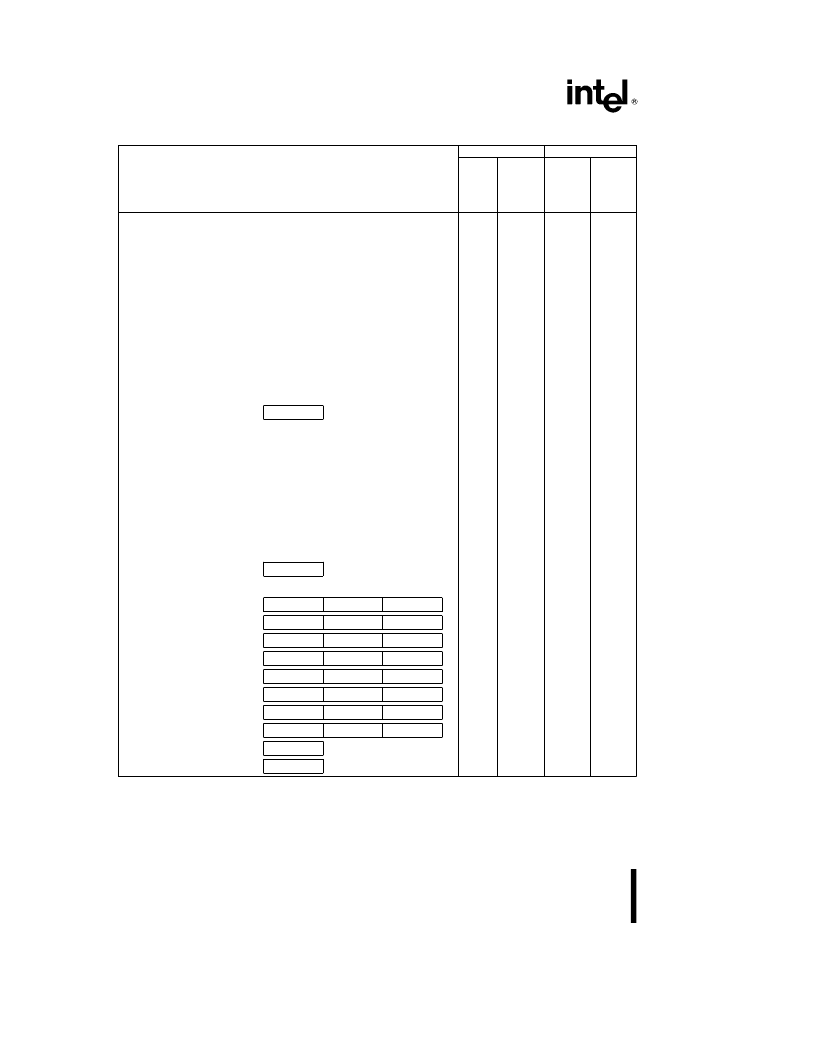

Table 9-1. Instruction Set Clock Count Summary

(Continued)

CLOCK COUNT

NOTES

Real

Address

Mode or

Virtual

8086

Mode

Real

Address

Mode or

Virtual

8086

Mode

INSTRUCTION

FORMAT

Protected

Virtual

Address

Mode

Protected

Virtual

Address

Mode

INTERRUPT INSTRUCTIONS

(Continued)

BOUND:

Via Interrupt or Trap Gate

to Same Privilege Level

Via Interrupt or Trap Gate

to Different Privilege Level

From 286 Task to 286 TSS via Task Gate

From 286 Task to Intel386

TM

SX CPU TSS via Task Gate

From 268 Task to virt 8086 Mode via Task Gate

From Intel386 SX CPU Task to 286 TSS via Task Gate

From Intel386 SX CPU Task to Intel386 SX CPU TSS via Task Gate

From Intel386 SX CPU Task to virt 8086 Mode via Task Gate

From virt 8086 Mode to 286 TSS via Task Gate

From virt 8086 Mode to Intel386 SX CPU TSS via Task Gate

From virt 8086 md to priv level 0 via Trap Gate or Interrupt Gate

71

g, j, k, r

111

358

388

335

368

398

347

368

398

223

g, j, k, r

g, j, k, r

g, j, k, r

g, j, k, r

g, j, k, r

g, j, k, r

g, j, k, r,

g, j, k, r

g, j, k, r

INTERRUPT RETURN

IRET

e

Interrupt Return

1 1 0 0 1 1 1 1

24

g, h, j, k, r

Protected Mode Only (IRET)

To the Same Privilege Level (within task)

To Different Privilege Level (within task)

From 286 Task to 286 TSS

From 286 Task to Intel386 SX CPU TSS

From 286 Task to Virtual 8086 Task

From 286 Task to Virtual 8086 Mode (within task)

From Intel386 SX CPU Task to 286 TSS

From Intel386 SX CPU Task to Intel386 SX CPU TSS

From Intel386 SX CPU Task to Virtual 8086 Task

From Intel386 SX CPU Task to Virtual 8086 Mode (within task)

42

86

285

318

267

113

324

328

377

113

g, h, j, k, r

g, h, j, k, r

h, j, k, r

h, j, k, r

h, j, k, r

h, j, k, r

h, j, k, r

h, j, k, r

PROCESSOR CONTROL

HLT

e

HALT

1 1 1 1 0 1 0 0

5

5

l

MOV

e

Move to and From Control/Debug/Test Registers

CR0/CR2/CR3 from register

0 0 0 0 1 1 1 1

0 0 1 0 0 0 1 0

1 1 eee reg

10/4/5

10/4/5

l

Register From CR0–3

0 0 0 0 1 1 1 1

0 0 1 0 0 0 0 0

1 1 eee reg

6

6

l

DR0–3 From Register

0 0 0 0 1 1 1 1

0 0 1 0 0 0 1 1

1 1 eee reg

22

22

l

DR6–7 From Register

0 0 0 0 1 1 1 1

0 0 1 0 0 0 1 1

1 1 eee reg

16

16

l

Register from DR6–7

0 0 0 0 1 1 1 1

0 0 1 0 0 0 0 1

1 1 eee reg

14

14

l

Register from DR0–3

0 0 0 0 1 1 1 1

0 0 1 0 0 0 0 1

1 1 eee reg

22

22

l

TR6–7 from Register

0 0 0 0 1 1 1 1

0 0 1 0 0 1 1 0

1 1 eee reg

12

12

l

Register from TR6–7

0 0 0 0 1 1 1 1

0 0 1 0 0 1 0 0

1 1 eee reg

12

12

l

NOP

e

No Operation

1 0 0 1 0 0 0 0

3

3

WAIT

e

Wait until BUSY

Y

pin is negated

1 0 0 1 1 0 1 1

6

6

92

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KU80C186EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC20 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KU-3C-110D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-120A | 制造商:M.E.C. Relays 功能描述: 制造商:Master Electronic Controls (MEC) 功能描述: |

| KU-3C-12A | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-12D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-240A | 制造商:M.E.C. Relays 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。