- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373200 > KU386 (Intel Corp.) SX MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | KU386 |

| 廠商: | Intel Corp. |

| 英文描述: | SX MICROPROCESSOR |

| 中文描述: | SX微處理器 |

| 文件頁數(shù): | 96/102頁 |

| 文件大小: | 1268K |

| 代理商: | KU386 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁當前第96頁第97頁第98頁第99頁第100頁第101頁第102頁

Intel386

TM

SX MICROPROCESSOR

9.2.2 32-Bit Extensions of the

Instruction Set

With the Intel386 SX CPU, the 8086/80186/80286

instruction set is extended in two orthogonal direc-

tions: 32-bit forms of all 16-bit instructions are added

to support the 32-bit data types, and 32-bit address-

ing modes are made available for all instructions ref-

erencing memory. This orthogonal instruction set ex-

tension is accomplished having a Default (D) bit in

the code segment descriptor, and by having 2 prefix-

es to the instruction set.

Whether the instruction defaults to operations of

16 bits or 32 bits depends on the setting of the D bit

in the code segment descriptor, which gives the de-

fault length (either 32 bits or 16 bits) for both oper-

ands and effective addresses when executing that

code segment. In the Real Address Mode or Virtual

8086 Mode, no code segment descriptors are used,

but a D value of 0 is assumed internally by the

Intel386 SX CPU when operating in those modes

(for 16-bit default sizes compatible with the 8086/

80186/80286).

Two prefixes, the Operand Size Prefix and the Effec-

tive Address Size Prefix, allow overriding individually

the Default selection of operand size and effective

address size. These prefixes may precede any op-

code bytes and affect only the instruction they pre-

cede. If necessary, one or both of the prefixes may

be placed before the opcode bytes. The presence of

the Operand Size Prefix and the Effective Address

Prefix will toggle the operand size or the effective

address size, respectively, to the value ‘‘opposite’’

from the Default setting. For example, if the default

operand size is for 32-bit data operations, then pres-

ence of the Operand Size Prefix toggles the instruc-

tion to 16-bit data operation. As another example, if

the default effective address size is 16 bits, pres-

ence of the Effective Address Size prefix toggles the

instruction to use 32-bit effective address computa-

tions.

These 32-bit extensions are available in all modes,

including the Real Address Mode or the Virtual 8086

Mode. In these modes the default is always 16 bits,

so prefixes are needed to specify 32-bit operands or

addresses. For instructions with more than one pre-

fix, the order of prefixes is unimportant.

Unless specified otherwise, instructions with 8-bit

and 16-bit operands do not affect the contents of

the high-order bits of the extended registers.

9.2.3 Encoding of Instruction Fields

Within the instruction are several fields indicating

register selection, addressing mode and so on. The

exact encodings of these fields are defined immedi-

ately ahead.

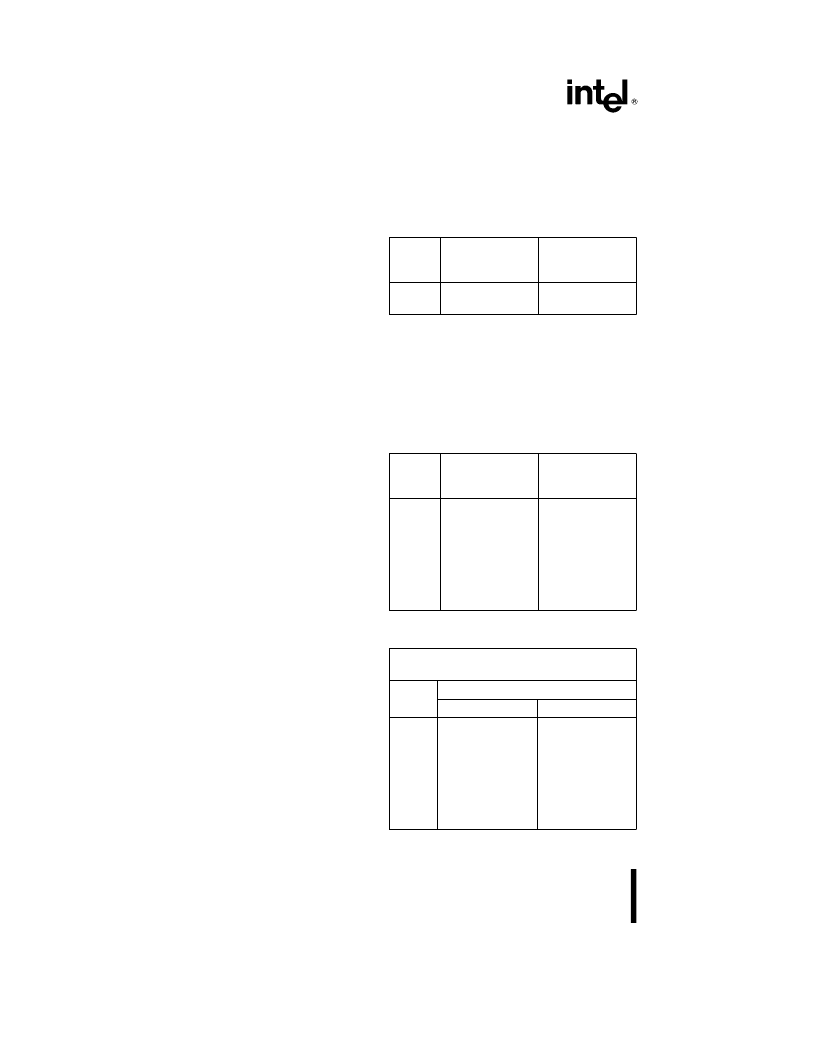

9.2.3.1 ENCODING OF OPERAND LENGTH (w)

FIELD

For any given instruction performing a data opera-

tion, the instruction is executing as a 32-bit operation

or a 16-bit operation. Within the constraints of the

operation size, the w field encodes the operand size

as either one byte or the full operation size, as

shown in the table below.

Operand Size

During 16-Bit

Data Operations

Operand Size

During 32-Bit

Data Operations

w Field

0

1

8 Bits

16 Bits

8 Bits

32 Bits

9.2.3.2 ENCODING OF THE GENERAL

REGISTER (reg) FIELD

The general register is specified by the reg field,

which may appear in the primary opcode bytes, or as

the reg field of the ‘‘mod r/m’’ byte, or as the r/m

field of the ‘‘mod r/m’’ byte.

Encoding of reg Field When w Field

is not Present in Instruction

Register Selected Register Selected

During 16-Bit

Data Operations

reg Field

During 32-Bit

Data Operations

000

001

010

011

100

101

101

101

AX

CX

DX

BX

SP

BP

SI

DI

EAX

ECX

EDX

EBX

ESP

EBP

ESI

EDI

Encoding of reg Field When w Field

is Present in Instruction

Register Specified by reg Field

During 16-Bit Data Operations:

reg

Function of w Field

(when w

e

0)

(when w

e

1)

000

001

010

011

100

101

110

111

AL

CL

DL

BL

AH

CH

DH

BH

AX

CX

DX

BX

SP

BP

SI

DI

96

相關PDF資料 |

PDF描述 |

|---|---|

| KU80C186EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC20 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| KU-3C-110D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-120A | 制造商:M.E.C. Relays 功能描述: 制造商:Master Electronic Controls (MEC) 功能描述: |

| KU-3C-12A | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-12D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-240A | 制造商:M.E.C. Relays 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。