- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373200 > KU386 (Intel Corp.) SX MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | KU386 |

| 廠商: | Intel Corp. |

| 英文描述: | SX MICROPROCESSOR |

| 中文描述: | SX微處理器 |

| 文件頁數(shù): | 26/102頁 |

| 文件大小: | 1268K |

| 代理商: | KU386 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

Intel386

TM

SX MICROPROCESSOR

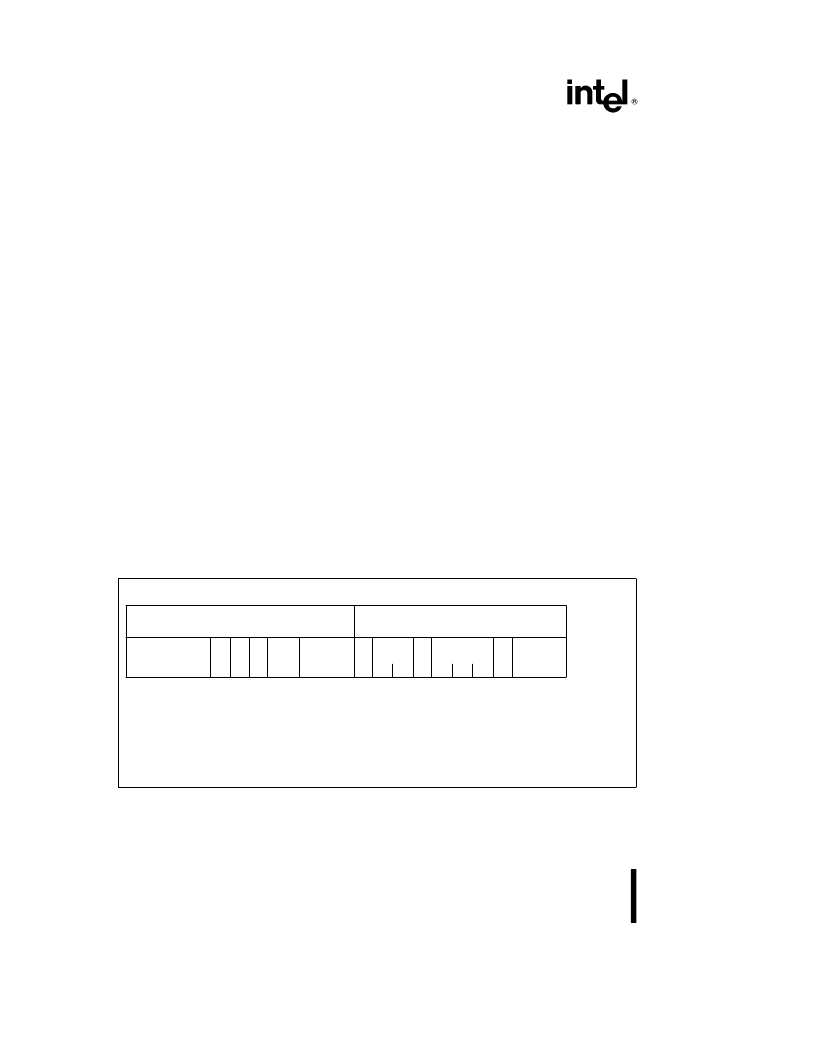

Each of the tables has a register associated with it:

GDTR, LDTR, and IDTR; see Figure 2.1. The LGDT,

LLDT, and LIDT instructions load the base and limit

of the Global, Local, and Interrupt Descriptor Tables

into the appropriate register. The SGDT, SLDT, and

SIDT store the base and limit values. These are priv-

ileged instructions.

Global Descriptor Table

The Global Descriptor Table (GDT) contains de-

scriptors which are available to all of the tasks in a

system. The GDT can contain any type of segment

descriptor except for interrupt and trap descriptors.

Every Intel386 SX CPU system contains a GDT.

The first slot of the Global Descriptor Table corre-

sponds to the null selector and is not used. The null

selector defines a null pointer value.

Local Descriptor Table

LDTs contain descriptors which are associated with

a given task. Generally, operating systems are de-

signed so that each task has a separate LDT. The

LDT may contain only code, data, stack, task gate,

and call gate descriptors. LDTs provide a mecha-

nism for isolating a given task’s code and data seg-

ments from the rest of the operating system, while

the GDT contains descriptors for segments which

are common to all tasks. A segment cannot be ac-

cessed by a task if its segment descriptor does not

exist in either the current LDT or the GDT. This pro-

vides both isolation and protection for a task’s seg-

ments while still allowing global data to be shared

among tasks.

Unlike the 6-byte GDT or IDT registers which contain

a base address and limit, the visible portion of the

LDT register contains only a 16-bit selector. This se-

lector refers to a Local Descriptor Table descriptor in

the GDT (see figure 2.1).

Interrupt Descriptor Table

The third table needed for Intel386 SX Microproces-

sor systems is the Interrupt Descriptor Table. The

IDT contains the descriptors which point to the loca-

tion of the up to 256 interrupt service routines. The

IDT may contain only task gates, interrupt gates, and

trap gates. The IDT should be at least 256 bytes in

size in order to hold the descriptors for the 32 Intel

Reserved Interrupts. Every interrupt used by a sys-

tem must have an entry in the IDT. The IDT entries

are referenced by INT instructions, external interrupt

vectors, and exceptions.

DESCRIPTORS

The object to which the segment selector points to

is called a descriptor. Descriptors are eight byte

quantities which contain attributes about a given re-

gion of linear address space. These attributes in-

clude the 32-bit base linear address of the segment,

the 20-bit length and granularity of the segment, the

protection level, read, write or execute privileges,

the default size of the operands (16-bit or 32-bit),

and the type of segment. All of the attribute informa-

tion about a segment is contained in 12 bits in the

segment descriptor. Figure 4.4 shows the general

format of a descriptor. All segments on the Intel386

SX Microprocessor have three attribute fields in

common: the P bit, the DPL bit, and the S bit. The P

31

0

BYTE

ADDRESS

SEGMENT BASE 15 . . . 0

SEGMENT LIMIT 15 . . . 0

0

BASE 31 . . . 24

G

D

0

AVL

LIMIT

19 . . . 16

P

DPL

S

TYPE

A

BASE

23 . . . 16

a

4

BASE

LIMIT

P

DPL

S

TYPE

A

G

D

0

AVL

Base Address of the segment

The length of the segment

Present Bit

1

e

Present

Descriptor Privilege Level 0–3

Segment Descriptor

Type of Segment

Accessed Bit

Granularity Bit

Default Operation Size (recognized in code segment descriptors only)

Bit must be zero (0) for compatibility with future processors

Available field for user or OS

0

e

Not Present

0

e

System Descriptor

1

e

Code or Data Segment Descriptor

1

e

Segment length is page granular

0

e

Segment length is byte granular

1

e

32-bit segment

0

e

16-bit segment

Figure 4.4. Segment Descriptors

26

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KU80C186EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80C188EC25 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC16 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| KU80L186EC20 | 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KU-3C-110D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-120A | 制造商:M.E.C. Relays 功能描述: 制造商:Master Electronic Controls (MEC) 功能描述: |

| KU-3C-12A | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-12D | 制造商:M.E.C. Relays 功能描述: |

| KU-3C-240A | 制造商:M.E.C. Relays 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。