- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374354 > KM416RD4C (SAMSUNG SEMICONDUCTOR CO. LTD.) Direct Rambus DRAM(Direct Rambus 動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | KM416RD4C |

| 廠(chǎng)商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | Direct Rambus DRAM(Direct Rambus 動(dòng)態(tài)RAM) |

| 中文描述: | 直接Rambus公司的DRAM(動(dòng)態(tài)內(nèi)存直接Rambus公司) |

| 文件頁(yè)數(shù): | 50/59頁(yè) |

| 文件大小: | 4654K |

| 代理商: | KM416RD4C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)當(dāng)前第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)

Page 51

KM416RD4C/KM418RD4C

Direct RDRAM

Revision 0.2 September 1998

TARGET

CMOS - Receive Timing

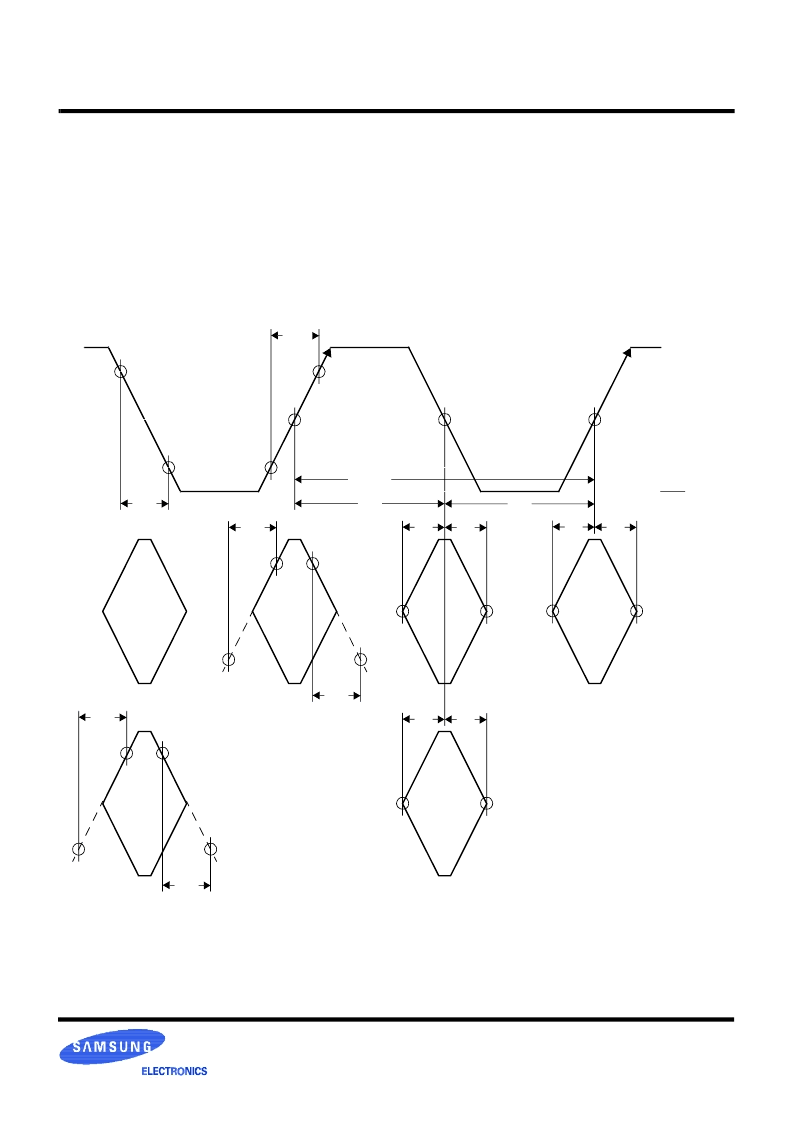

Figure Figure is a timing diagram which shows the detailed

requirements for the CMOS input signals .

The CMD and SIO0 signals are inputs which receive infor-

mation transmitted by a controller (or by another RDRAM’s

SIO1 output. SCK is the CMOS clock signal driven by the

controller. All signals are high true.

The cycle time, high phase time, and low phase time of the

SCK clock are t

CYCLE1

, t

CH1

and t

CL1

, all measured at the

50% level. The rise and fall times of SCK, CMD, and SIO0

are t

DR1

and t

DF1

, measured at the 20% and 80% levels.

The CMD signal is sampled twice per t

CYCLE1

interval, on

the rising edge (odd data) and the falling edge (even data).

The set/hold window of the sample points is t

S1

/t

H1.

The

SCK and CMD timing points are measured at the 50% level.

The SIO0 signal is sampled once per t

CYCLE1

interval on the

falling edge. The set/hold window of the sample points is

t

S2

/t

H2.

The SCK and SIO0 timing points are measured at the

50% level.

Figure 55 : CMOS Timing - Data Signals for Receive

V

IH,CMOS

50%

V

IL,CMOS

80%

20%

SCK

t

S1

CMD

t

DR2

t

H1

t

S1

t

H1

even

odd

t

DF2

V

IH,CMOS

50%

V

IL,CMOS

80%

20%

t

DR2

t

DF2

t

CH1

t

CL1

t

CYCLE1

t

S2

SIO0

t

DR1

t

H2

t

DF1

V

IH,CMOS

50%

V

IL,CMOS

80%

20%

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM416S1021CT-G7 | 512K x 16Bit x 2 Banks Synchronous DRAM with SSTL interface |

| KM416S1021CT-G8 | 512K x 16Bit x 2 Banks Synchronous DRAM with SSTL interface |

| KM416S1021CT-GS | 512K x 16Bit x 2 Banks Synchronous DRAM with SSTL interface |

| KM416S1120D | 512K x 16bit x 2 Banks Synchronous DRAM LVTTL |

| KM416S16230A | 4M x 16Bit x 4 Banks Synchronous DRAM(4M x 16位 x4組同步動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM416RD4D | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD8AC | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD8AC(D)-RK70 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD8AC(D)-RK80 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD8AC(DB)-RCG60 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。