- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360868 > IP100 PCI 10/100M Single Chip Ethernet Controller PDF資料下載

參數(shù)資料

| 型號(hào): | IP100 |

| 英文描述: | PCI 10/100M Single Chip Ethernet Controller |

| 中文描述: | 單芯片的PCI個(gè)10/100M以太網(wǎng)控制器 |

| 文件頁(yè)數(shù): | 52/92頁(yè) |

| 文件大小: | 2801K |

| 代理商: | IP100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)當(dāng)前第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

IP100

Note: External loopback is controlled by the PHY. To utilize external loopback, the host system must enable a

loopback mode within the PHY using the MII Management Interface. For the true “on-the-wire” loopback mode,

use a loopback plug (connector), clear the FIFOLoopback, and MACLoopback and any PHY loopback bits to zero,

set the FullDuplexEnable bit to a logic 1, and enable the full duplex mode within the PHY.

10.4.19 MACCtrl1

Class............................. LAN I/O Registers, Control and Status

Base Address ............... IoBaseAddress register value

Address Offset .............. 0x52

Default .......................... 0x0000

Width ............................ 16 bits

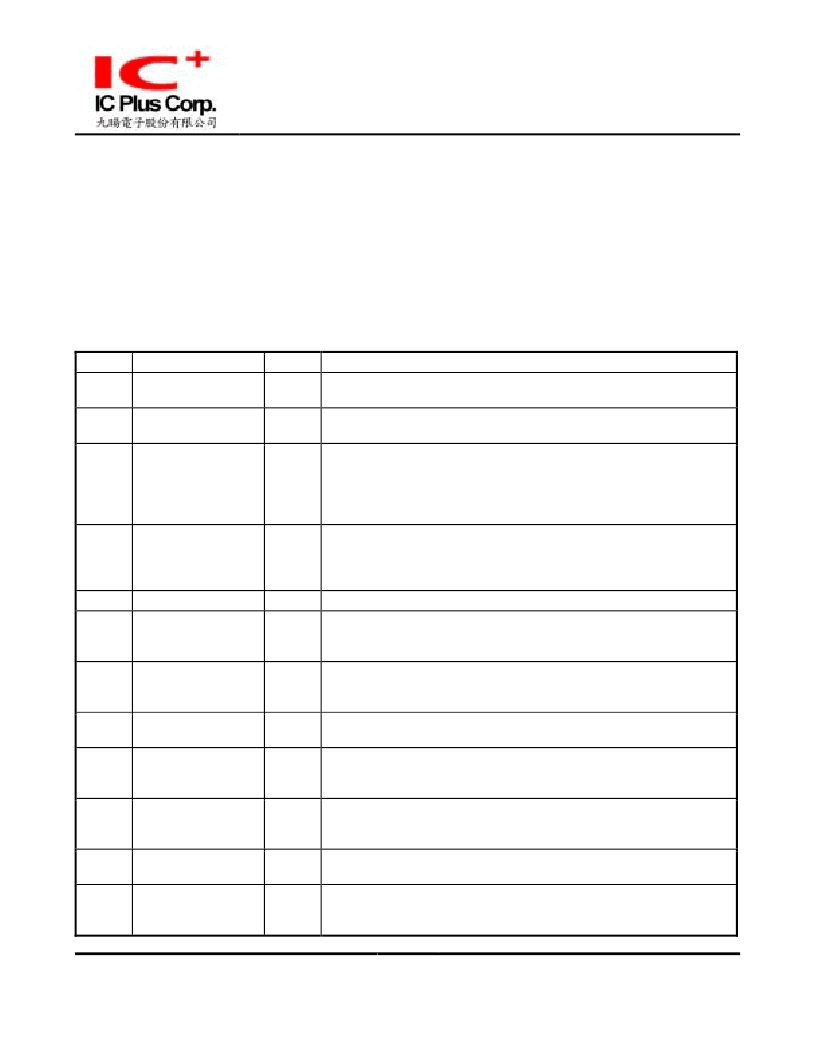

BIT

BIT NAME

R/W

0

CollisionDetect

R

Collision Detect. CollisionDetect provides a real-time indication of

the state of the COL signal within the IP100.

1

CarrierSense

R

Carrier Sense. CarrierSense provides a real-time indication of the

state of the CRS signal within IP100.

2

TxInProg

R

Transmit In Progress. TxInProg provides a real-time indication that a

frame is being transmitted. If TxInProg is a logic 1, a frame

transmission is in progress. TxInProg is used by the host system

during under run recovery to delay before setting the issuing a

TxReset bit in the AsicCtrl register.

3

TxError

R

Transmit Error. If a transmit under run occurs (indicated via the

TxUnderrun bit of the TxStatus register), TxError is a logic 1,

indicating that the transmitter needs to be reset via the TxReset bit

in the AsicCtrl register.

4

Reserved

N/A

Reserved for future use.

5

StatisticsEnable

W

Statistics Enable. Writing a logic 1 to StatisticsEnable will enable the

IP100’s statistic registers. The state (enabled/disabled) of the

IP100’s statistic registers is shown via StatisticsEnabled.

6

StatisticsDisable

W

Statistics Disable. Writing a logic 1 to StatisticsDisable will disable

the IP100’s statistic registers. The state (enabled/disabled) of the

IP100’s statistic registers is shown via StatisticsEnabled.

7

StatisticsEnabled

R

Statistics Enabled. If StatisticsEnabled is a logic 1, the IP100’s

statistic registers are enabled.

8

TxEnable

W

Transmit Enable. Writing a logic 1 to TxEnable will enable the IP100

to transmit frames. The state (enabled/disabled) of the IP100’s

transmitter is shown via TxEnabled.

9

TxDisable

W

Transmit Disable. Writing a logic 1 to TxDisable will disable the

IP100 from transmitting frames. The state (enabled/disabled) of the

IP100’s transmitter is shown via TxEnabled.

10

TxEnabled

R

Transmit Enabled. If TxEnabled is a logic 1, the IP100’s transmitter

is enabled.

11

RxEnable

W

Receive Enable. Writing a logic 1 to RxEnable will enable the IP100

to receive frames. The state (enabled/disabled) of the IP100’s

receiver is shown via RxEnabled.

Copyright

2003, IC Plus Corp.

All rights reserved.

Preliminary, Specification subject to change without notice.

52/92

IP100-DS-R03

May 27, 2003

BIT DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP101 | PHY 10/100M Single Chip Fast Ethernet Transceiver |

| IP1060AD | Analog IC |

| IP1060AJ | Voltage-Mode SMPS Controller |

| IP1060AN | Analog IC |

| IP1060BJ | Voltage-Mode SMPS Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IP1000A | 制造商:IC PLUS 功能描述:IP1000A |

| IP1000ALF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

| IP1000ALF-DS-R01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

| IP1000ALF-DS-R02 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

| IP1000ALF-DS-R03 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Gigabit Ethernet NIC Single Chip |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。