- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295065 > AM79C965KCW (ADVANCED MICRO DEVICES INC) 3 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQFP16 PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C965KCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 3 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQFP16 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁(yè)數(shù): | 6/220頁(yè) |

| 文件大小: | 1197K |

| 代理商: | AM79C965KCW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)

P R E L I M I N A R Y

AMD

103

Am79C965

Software Access

I/O Resources

PCnet-32 Controller I/O Resource Mapping

The PCnet-32 controller has several I/O resources.

These resources use 32 bytes of I/O space that begin at

the PCnet-32 controller I/O Base Address.

The PCnet-32 controller allows two modes of slave ac-

cess. Word I/O mode treats all PCnet-32 controller I/O

Resources as two-byte entities spaced at two-byte ad-

dress intervals. Double Word I/O mode treats all

PCnet-32 controller I/O Resources as four-byte entities

spaced at four-byte address intervals. The selection

of WIO or DWIO mode is accomplished by one of

two ways:

1) H_RESET function.

The PCnet-32 controller I/O mode setting will default

to WIO after H_RESET (i.e. DWIO =0).

2) Automatic determination of DWIO mode due to

doubleword I/O write access to offset 10h.

DWIO is automatically programmed as active when the

system attempts a double word write access to offset

10h of the PCnet-32 controller I/O space. Note that this

space corresponds to RDP, regardless of whether

DWIO or WIO mode has been programmed. The power

up H_RESET value of DWIO will be ZERO, and this

value will be maintained until a double word access is

performed to PCnet-32 controller I/O space.

Therefore, if DWIO mode is desired, it is imperative that

the first access to the PCnet-32 controller be a double

word write access to offset 10h.

Alternatively, if DWIO mode is not desired, then it is im-

perative that the software never executes a double word

write access to offset 10h of the PCnet-32 controller I/O

space.

Once the DWIO bit has been set to a ONE, only a

H_RESET can reset it to a ZERO.

The DWIO mode setting is unaffected by S_RESET or

the STOP bit.

WIO I/O Resource Map

When the PCnet-32 controller I/O space is mapped as

Word I/O, then the resources that are allotted to the

PCnet-32 controller occur on word boundaries that are

offset from the PCnet-32 controller I/O Base Address as

shown in Table 32.

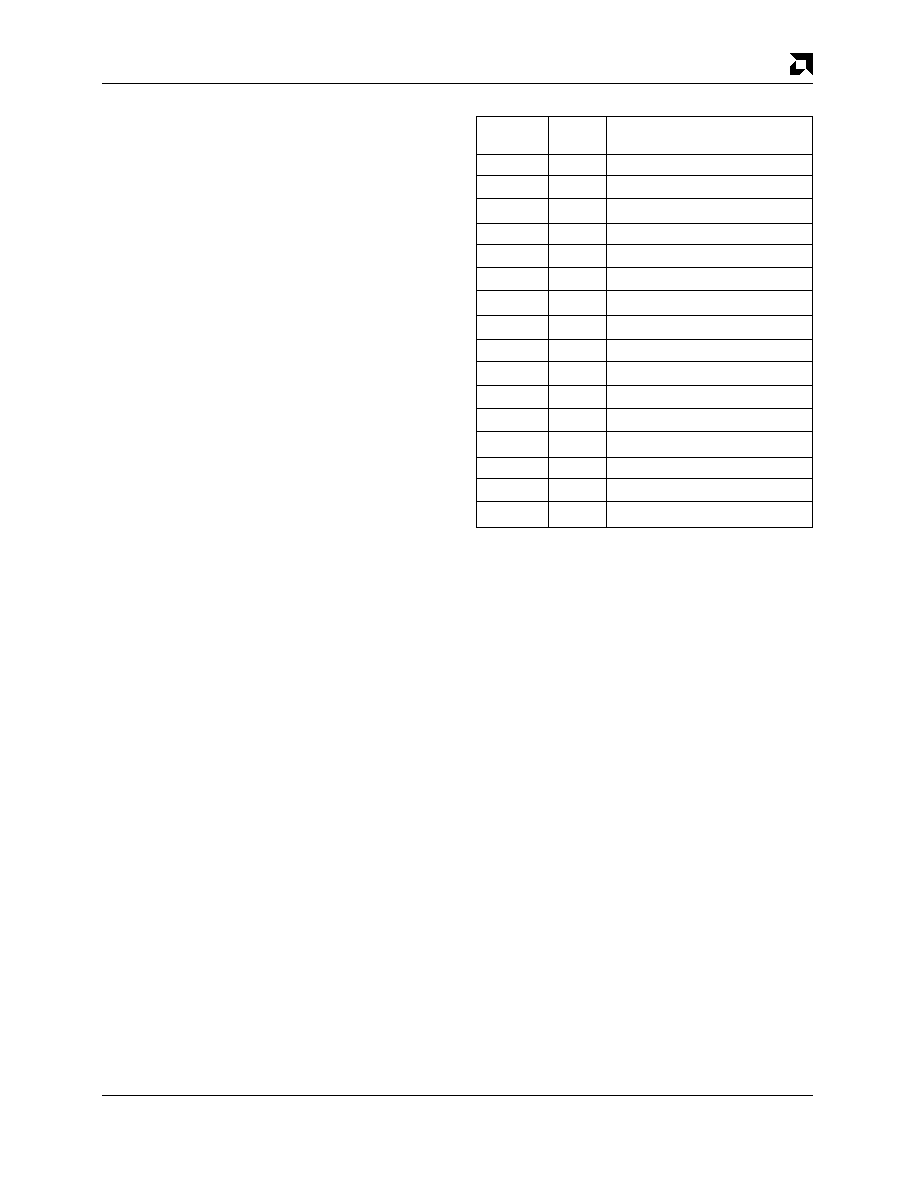

Table 32. Word I/O Mapping

Offset

No. of

(Hex)

Bytes

Register

0

2

Address PROM

2

Address PROM

4

2

Address PROM

6

2

Address PROM

8

2

Address PROM

A

2

Address PROM

C

2

Address PROM

E

2

Address PROM

10

2

RDP

12

2

RAP (shared by RDP and BDP)

14

2

Reset Register

16

2

BDP

18

2

Vendor Specific Word

1A

2

Reserved

1C

2

Reserved

1E

2

Reserved

When PCnet-32 controller I/O space is Word mapped,

all I/O resources fall on word boundaries and all I/O re-

sources are word quantities. However, while in Word I/O

mode, address PROM accesses may also be accessed

as individual bytes on byte addresses.

Attempts to write to any PCnet-32 controller I/O re-

sources (except to offset 10h, RDP) as 32 bit

quantities while in Word I/O mode are illegal and may

cause unexpected reprogramming of the PCnet-32 con-

troller control registers. Attempts to read

from any

PCnet-32 controller I/O resources as 32 bit quantities

while in Word I/O mode are illegal and will yield

undefined values.

An attempt to

write to offset 10H (RDP) as a 32 bit quan-

tity while in Word I/O mode will cause the PCnet-32 con-

troller to exit WIO mode and immediately thereafter, to

enter DWIO mode.

Accesses to non-word address boundaries are not al-

lowed while in WIO mode, with the exception of the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM80A-024L-120F18 | 1-OUTPUT 240 W DC-DC REG PWR SUPPLY MODULE |

| AJ80A-024L-033F50 | 1-OUTPUT 240 W DC-DC REG PWR SUPPLY MODULE |

| AM93LC66S | 4096-bits Serial Electrically Erasable PROM |

| AM93LC66SA | 4096-bits Serial Electrically Erasable PROM |

| AM93LC66VN | 4096-bits Serial Electrically Erasable PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C970 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus |

| AM79C970A | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC\\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。