- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄295065 > AM79C965KCW (ADVANCED MICRO DEVICES INC) 3 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQFP16 PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C965KCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 3 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQFP16 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁(yè)數(shù): | 81/220頁(yè) |

| 文件大?。?/td> | 1197K |

| 代理商: | AM79C965KCW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)當(dāng)前第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)

P R E L I M I N A R Y

AMD

171

Am79C965

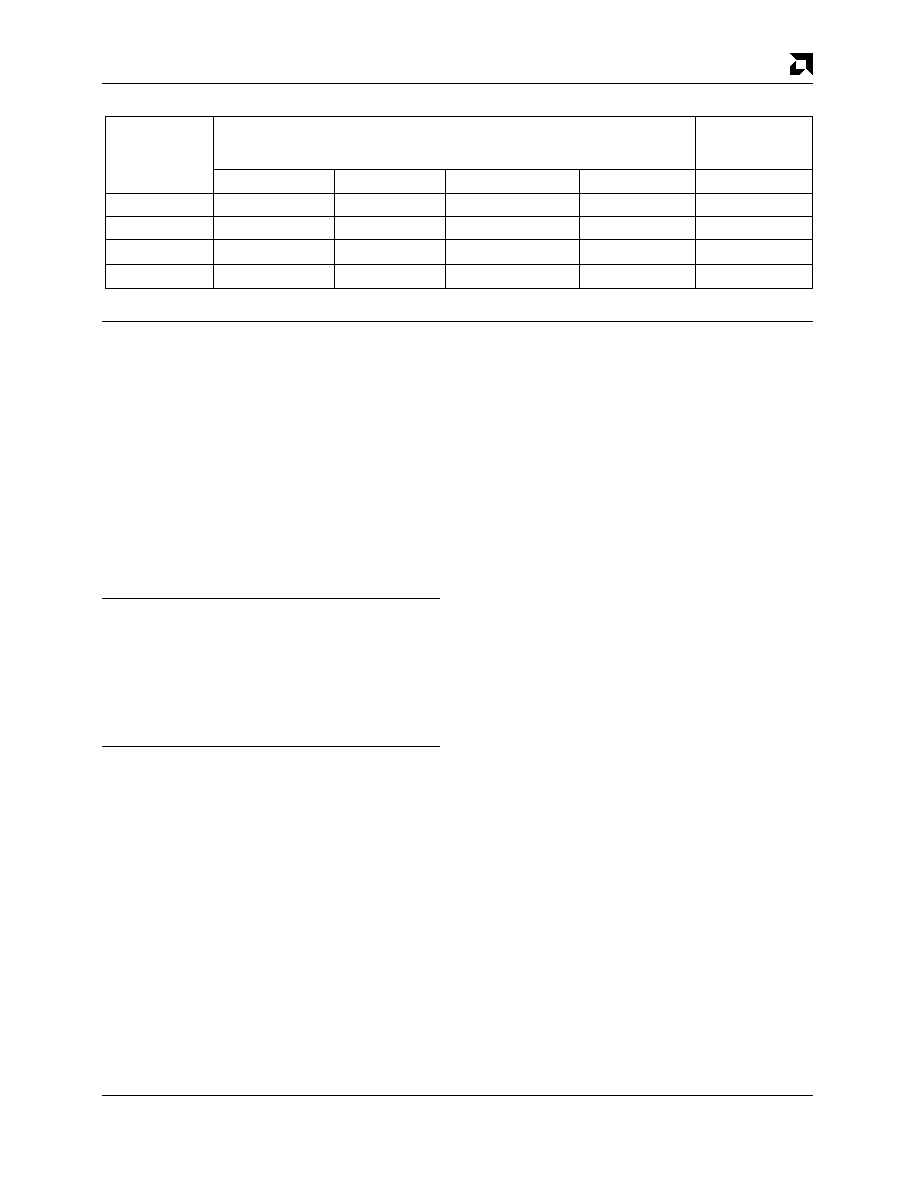

Table 60. Receive Descriptor (SSIZE32 =1)

PCnet-32

Descriptor

Designation

Address

Bits 31-24

Bits 23-16

Bits 15-8

Bits 7-0

Bits 31-0

CRDA+00

*NA

RMD1[7:0]

RMD0[15:8]

RMD0[7:0]

RMD0

CRDA+04

RMD1[15:8]

*NA

RMD2[15:8]

RMD2[7:0]

RMD1

CRDA+08

*NA

RMD3[15:8]

RMD3[7:0]

RMD2

CRDA+0C

*NA

RMD3

LANCE/PCnet-ISA

Descriptor Designation

*NA = These 8 bits do not exist in any LANCE descriptor.

The Receive Descriptor Ring Entries (RDREs) are com-

posed of four receive message descriptors (RMD0–

RMD3). Together they contain the following information:

s The address of the actual message data buffer in

user (host) memory.

s The length of that message buffer.

s Status information indicating the condition of the

buffer. The eight most significant bits of RMD1

(RMD1[31:24]) are collectively termed the STATUS

of the receive descriptor.

RMD0

Bit

Name

Description

31-0

RBADR

RECEIVE BUFFER ADDRESS.

This field contains the address of

the receive buffer that is associ-

ated with this descriptor.

RMD1

Bit

Name

Description

31

OWN

This bit indicates that the de-

scriptor entry is owned by the

host

(OWN=0)

or

by

the

PCnet-32 controller (OWN=1).

The PCnet-32 controller clears

the OWN bit after filling the buffer

pointed to by the descriptor entry.

The host sets the OWN bit after

emptying the buffer. Once the

PCnet-32 controller or host has

relinquished

ownership

of

a

buffer, it must not change any

field in the descriptor entry.

30

ERR

ERR is the OR of FRAM, OFLO,

CRC, or BUFF. ERR is set by the

PCnet-32 controller and cleared

by the host.

29

FRAM

FRAMING

ERROR

indicates

that the incoming frame con-

tained a non-integer multiple of

eight bits and there was an FCS

error. If there was no FCS error

on the incoming frame, then

FRAM will not be set even if there

was a non integer multiple of

eight bits in the frame. FRAM is

not valid in internal loopback

mode. FRAM is valid only when

ENP is set and OFLO is not.

FRAM is set by the PCnet-32

controller and cleared by the

host.

28

OFLO

OVERFLOW error indicates that

the receiver has lost all or part of

the incoming frame, due to an in-

ability to store the frame in a

memory buffer before the inter-

nal FIFO overflowed. OFLO is

valid only when ENP is not set.

OFLO is set by the PCnet-32

controller and cleared by the

host.

27

CRC

CRC indicates that the receiver

has detected a CRC (FCS) error

on the incoming frame. CRC is

valid only when ENP is set and

OFLO is not. CRC is set by the

PCnet-32 controller and cleared

by the host.

26

BUFF

BUFFER ERROR is set any time

the PCnet-32 controller does not

own the next buffer while data

chaining a received frame. This

can occur in either of two ways:

1) The OWN bit of the next

buffer is zero.

2) FIFO overflow occurred be-

fore the PCnet-32 controller

received

the

STATUS

(RMD1[31:24]) of the next de-

scriptor.

If a Buffer Error occurs, an Over-

flow Error may also occur inter-

nally in the FIFO, but will not be

reported in the descriptor status

entry unless both BUFF and

OFLO errors occur at the same

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM80A-024L-120F18 | 1-OUTPUT 240 W DC-DC REG PWR SUPPLY MODULE |

| AJ80A-024L-033F50 | 1-OUTPUT 240 W DC-DC REG PWR SUPPLY MODULE |

| AM93LC66S | 4096-bits Serial Electrically Erasable PROM |

| AM93LC66SA | 4096-bits Serial Electrically Erasable PROM |

| AM93LC66VN | 4096-bits Serial Electrically Erasable PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C970 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus |

| AM79C970A | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC\\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。