- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371179 > T8110 Version History PDF資料下載

參數(shù)資料

| 型號(hào): | T8110 |

| 英文描述: | Version History |

| 中文描述: | 版本歷史 |

| 文件頁(yè)數(shù): | 214/222頁(yè) |

| 文件大小: | 2343K |

| 代理商: | T8110 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)當(dāng)前第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)

212

Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador T8110 PCI-Based H.100/H.110 Switch

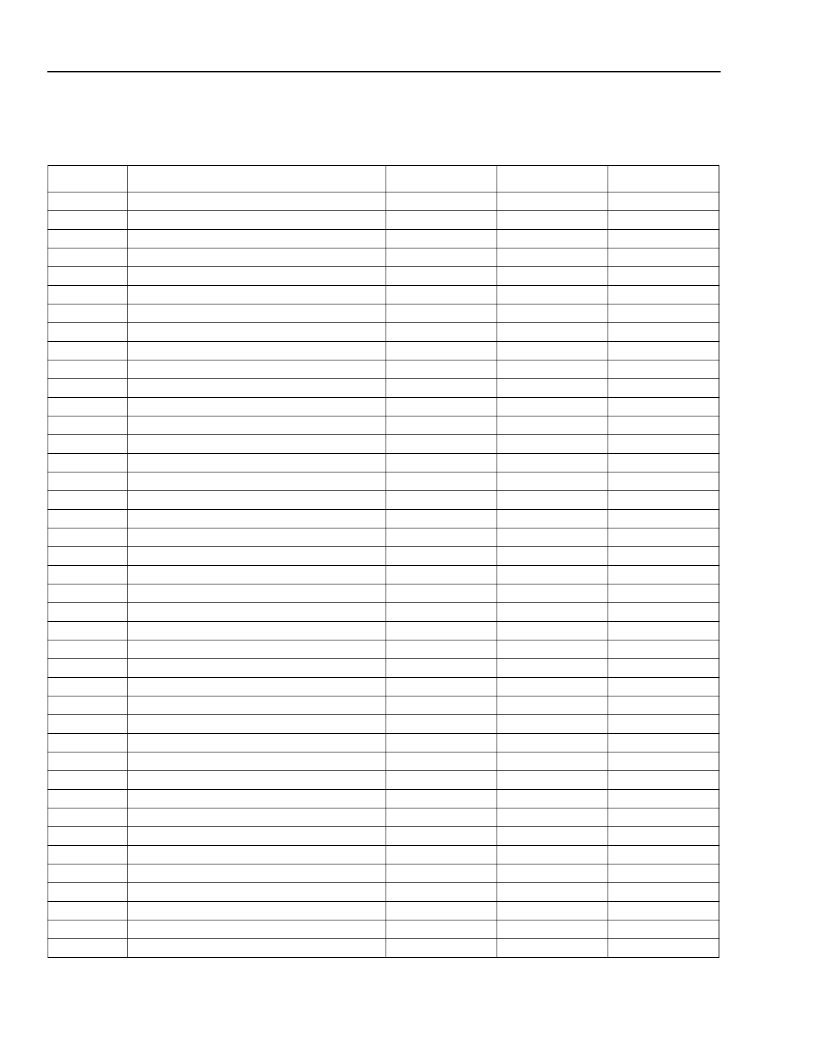

Appendix B. Register Bit Field Mnemonic Summary

(continued)

LDRSN

LERSN

LFRSN

LGRSN

LHRSN

F0LLR

F0ULR

F0ISB

F0WSP

F0RSR

F1LLR

F1ULR

F1ISB

F1WSP

F1RSR

F2LLR

F2ULR

F2ISB

F2WSP

F2RSR

F3LLR

F3ULR

F3ISB

F3WSP

F3RSR

F4LLR

F4ULR

F4ISB

F4WSP

F4RSR

F5LLR

F5ULR

F5ISB

F5WSP

F5RSR

F6LLR

F6ULR

F6ISB

F6WSP

F6RSR

F7LLR

Local group D rate

Local group E rate

Local group F rate

Local group G rate

Local group H rate

Frame 0 lower start time

Frame 0 upper start time

Frame 0 pulse inversion

Frame 0 pulse width

Frame 0 pulse width rate

Frame 1 lower start time

Frame 1 upper start time

Frame 1 pulse inversion

Frame 1 pulse width

Frame 1 pulse width rate

Frame 2 lower start time

Frame 2 upper start time

Frame 2 pulse inversion

Frame 2 pulse width

Frame 2 pulse width rate

Frame 3 lower start time

Frame 3 upper start time

Frame 3 pulse inversion

Frame 3 pulse width

Frame 3 pulse width rate

Frame 4 lower start time

Frame 4 upper start time

Frame 4 pulse inversion

Frame 4 pulse width

Frame 4 pulse width rate

Frame 5 lower start time

Frame 5 upper start time

Frame 5 pulse inversion

Frame 5 pulse width

Frame 5 pulse width rate

Frame 6 lower start time

Frame 6 upper start time

Frame 6 pulse inversion

Frame 6 pulse width

Frame 6 pulse width rate

Frame 7 lower start time

Select

Select

Select

Select

Select

Load

Load

Enable

Select

Select

Load

Load

Enable

Select

Select

Load

Load

Enable

Select

Select

Load

Load

Enable

Select

Select

Load

Load

Enable

Select

Select

Load

Load

Enable

Select

Select

Load

Load

Enable

Select

Select

Load

0x00321

0x00322

0x00322

0x00323

0x00323

0x00400

0x00401

0x00402

0x00402

0x00403

0x00410

0x00411

0x00412

0x00412

0x00413

0x00420

0x00421

0x00422

0x00422

0x00423

0x00430

0x00431

0x00432

0x00432

0x00433

0x00440

0x00441

0x00442

0x00442

0x00443

0x00450

0x00451

0x00452

0x00452

0x00453

0x00460

0x00461

0x00462

0x00462

0x00463

0x00470

U

L

U

L

U

—

—

7

6:0

—

—

—

7

6:0

—

—

—

7

6:0

—

—

—

7

6:0

—

—

—

7

6:0

—

—

—

7

6:0

—

—

—

7

6:0

—

—

Table 134. Mnemonic Summary, Sorted by Register

(continued)

Mnemonic

Description

Type

Register

Bit Position

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8301 | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8502 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8503 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8531A | T8531A/8532 Multichannel Programmable Codec Chip Set |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T811004 | 制造商:E-SWITCH 制造商全稱(chēng):E-SWITCH 功能描述:E-SWITCH 800SP9B5M2QE |

| T-8110---BAL-DB | 制造商:LSI Corporation 功能描述:Switch Fabric 4K x 4K 3.3V 272-Pin BGA |

| T8110L | 制造商:AGERE 制造商全稱(chēng):AGERE 功能描述:Ambassador㈢ T8110L H.100/H.110 Switch |

| T-8110L | 制造商:AGERE 制造商全稱(chēng):AGERE 功能描述:Ambassador㈢ T8110L H.100/H.110 Switch |

| T81110 | 制造商:Allied Controls Incorporated 功能描述:Conn Relay Socket SKT 8 POS Solder Lug ST Panel Mount |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。