- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄179201 > LP3-E5B321A (OTTO ENGINEERING INC) PUSHBUTTON SWITCH, SPST, MOMENTARY, PANEL MOUNT-THREADED PDF資料下載

參數(shù)資料

| 型號: | LP3-E5B321A |

| 廠商: | OTTO ENGINEERING INC |

| 元件分類: | 開關 |

| 英文描述: | PUSHBUTTON SWITCH, SPST, MOMENTARY, PANEL MOUNT-THREADED |

| 文件頁數(shù): | 3/3頁 |

| 文件大小: | 811K |

| 代理商: | LP3-E5B321A |

LIGHTED AND SEALED PUSHBUTTONS

LIGHTED

PUSHBUTTONS

LP3

44

OTTO 2007 Full Line Catalog

Specifications Subject To Change Without Notice

COMMERCIAL GRADE LED LIGHTED AND SEALED AGAINST DUST AND MOISTURE

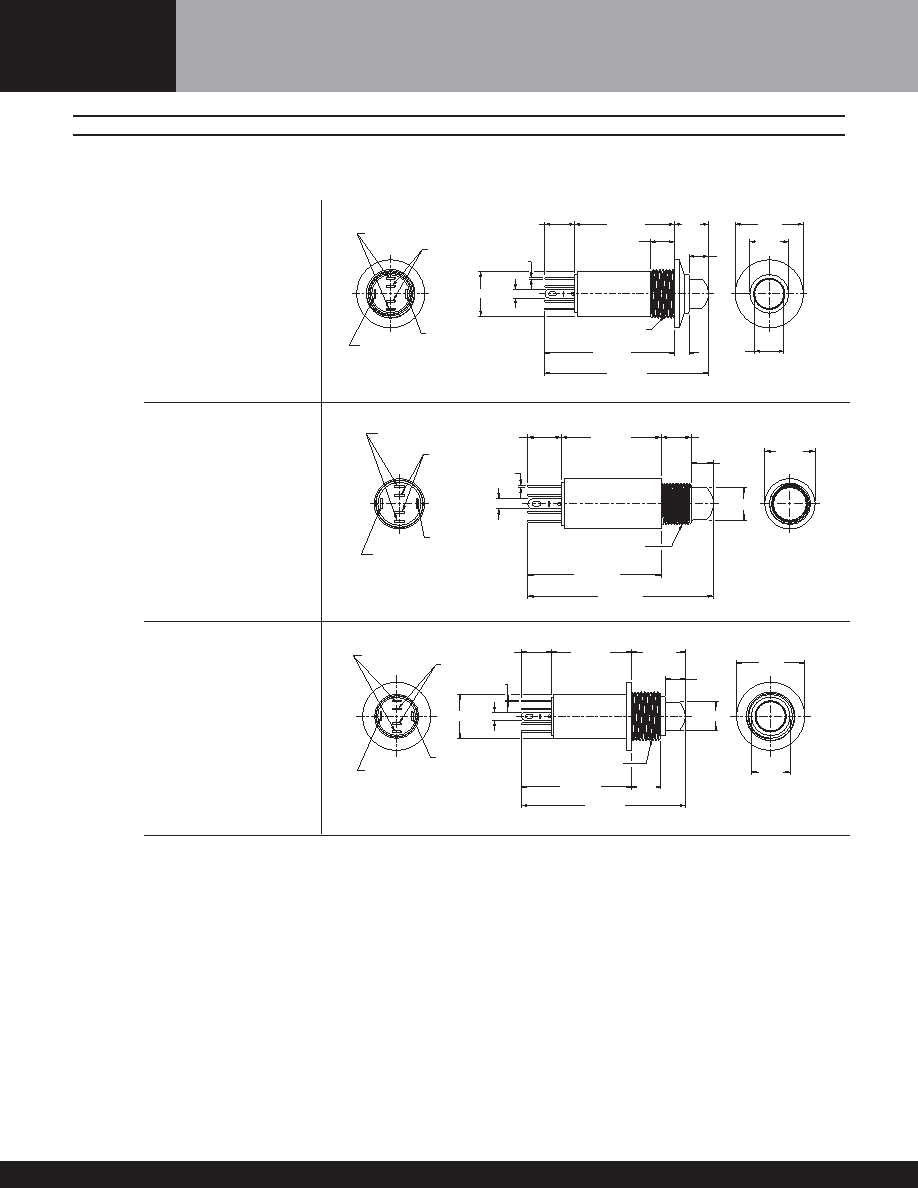

NORMALLY OPEN

TERMINALS

NORMALLY CLOSED

TERMINALS

LED ANODE (+)

LED CATHODE (-)

.570

.110 (TYP)

.020 (TYP)

1.033 REF.

.687 REF.

2.150 MAX.

1.463 MAX.

.375

.375

.25

.875

.500

.380 REF.

.625-24 UNEF-2A THD. TO

WITHIN .062 OF FLANGE

LP3-6

Momentary, 5/8” Threaded Rear Mount

NOTE:

For indicator light only, see LP5 series

NORMALLY OPEN

TERMINALS

NORMALLY CLOSED

TERMINALS

.570

LED ANODE (+)

LED CATHODE (-)

.110 (TYP)

.020 (TYP)

1.283 REF.

1.713 MAX.

.187

.375

.875

.500

2.150 MAX.

.437

REF.

.310

.25

.380 REF.

.625-24 UNEF-2A THD. TO

WITHIN .062 OF FLANGE

NORMALLY OPEN

TERMINALS

NORMALLY CLOSED

TERMINALS

LED ANODE (+)

LED CATHODE (-)

.110 (TYP)

.020 (TYP)

1.130 REF.

2.150 MAX.

1.560 MAX.

.375

.34

.25

.570

.380 REF.

.469-32 UNS-2A THD. TO

WITHIN .062 OF FLANGE

LP3-3

Momentary, 5/8” Threaded Front Mount

LP3-4

Momentary, 15/32” Threaded Rear Mount

相關PDF資料 |

PDF描述 |

|---|---|

| LP3-E5M121A | PUSHBUTTON SWITCH, SPST, MOMENTARY, PANEL MOUNT-THREADED |

| LP3-E6M152A | PUSHBUTTON SWITCH, SPDT, MOMENTARY, PANEL MOUNT-THREADED |

| LP3-E6M251W | PUSHBUTTON SWITCH, SPDT, MOMENTARY, PANEL MOUNT-THREADED |

| LP3-F4B121W | PUSHBUTTON SWITCH, SPST, MOMENTARY, PANEL MOUNT-THREADED |

| LP3-F4B151W | PUSHBUTTON SWITCH, SPST, MOMENTARY, PANEL MOUNT-THREADED |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LP3-E6G322R | 功能描述:按鈕開關 Exposed Dome SPDT 12V Red LED RoHS:否 制造商:OTTO 觸點形式: 開關功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 安裝風格: 照明: 照明顏色: IP 等級: 端接類型: 觸點電鍍: 執(zhí)行器: 蓋顏色: 封裝: 可燃性等級: |

| LP3-F000011 | 制造商:OTTO Engineering Inc 功能描述:LP3-F4A322W WITH |

| LP3-F1A321W | 功能描述:按鈕開關 Flush Dome SPST 2V Red LED RoHS:否 制造商:OTTO 觸點形式: 開關功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 安裝風格: 照明: 照明顏色: IP 等級: 端接類型: 觸點電鍍: 執(zhí)行器: 蓋顏色: 封裝: 可燃性等級: |

| LP3-F1A322R | 功能描述:按鈕開關 Flush Dome SPST 2V Red LED RoHS:否 制造商:OTTO 觸點形式: 開關功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 安裝風格: 照明: 照明顏色: IP 等級: 端接類型: 觸點電鍍: 執(zhí)行器: 蓋顏色: 封裝: 可燃性等級: |

| LP3-F1B322W | 功能描述:按鈕開關 Flush Dome SPST 2V Green LED RoHS:否 制造商:OTTO 觸點形式: 開關功能: 電流額定值: 電壓額定值 AC: 電壓額定值 DC: 功率額定值: 安裝風格: 照明: 照明顏色: IP 等級: 端接類型: 觸點電鍍: 執(zhí)行器: 蓋顏色: 封裝: 可燃性等級: |

發(fā)布緊急采購,3分鐘左右您將得到回復。