- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8302 T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q PDF資料下載

參數(shù)資料

| 型號(hào): | T8302 |

| 英文描述: | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| 中文描述: | T8302因特網(wǎng)協(xié)議電話高級(jí)RISC機(jī)(ARM)的以太網(wǎng)使用IEEE 802.1q的服務(wù)質(zhì)量 |

| 文件頁(yè)數(shù): | 138/248頁(yè) |

| 文件大?。?/td> | 7321K |

| 代理商: | T8302 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)當(dāng)前第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)第234頁(yè)第235頁(yè)第236頁(yè)第237頁(yè)第238頁(yè)第239頁(yè)第240頁(yè)第241頁(yè)第242頁(yè)第243頁(yè)第244頁(yè)第245頁(yè)第246頁(yè)第247頁(yè)第248頁(yè)

136

Agere Systems Inc.

T8302 Internet Protocol Telephone

Advanced RISC Machine (

ARM

)

Data Sheet

July 2001

11 10/100 2-Port Repeater and Backplane Segment Controller

(continued)

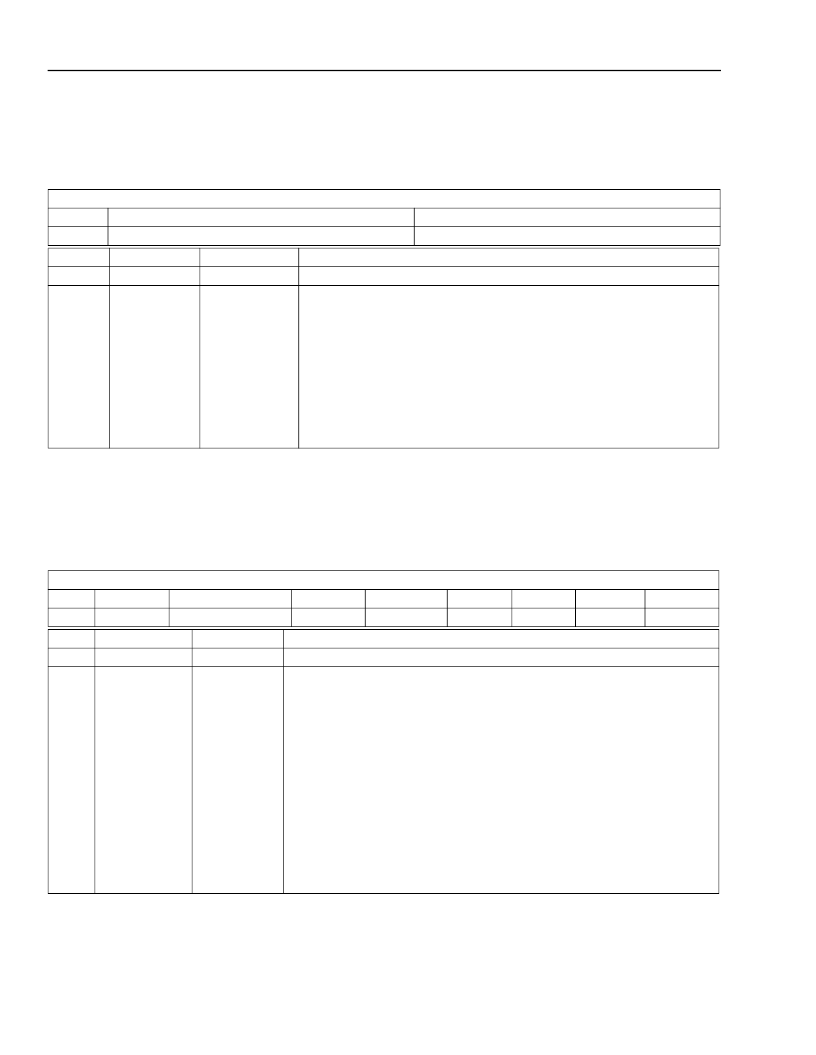

11.5.3 Port Control Registers, for Port 0, 1

Table 116. Port Control Registers for Port 0, 1

11.5.4 Port Configuration Register 0 for Port 0, 1

This register is used to configure the repeater port as described below. This register will default to the values in

parenthesis after reset.

Table 117. Port Configuration Register 0 for Port 0, 1

Address—Port 0 (0xE001 2020), Port 1 (0xE001 2220)

31:1

RSVD

State on RST

(0)

Reserved.

(0)

Software reset. When this bit is set to 1, the port repeater digital cir-

cuits are reset to the power-on state.

Bit #

Name

Bit #

31:1

0

SRST

Name

RSVD

SRST

Description

0

Note:

This bit is provided primarily for diagnostic and debugging pur-

poses and is

not

intended to be used in place of the

RESET

pin at system start-up. A full hardware reset is required to

place the entire chip in a known state. All registers will retain

their values.

Write

1

to reset.

Write 0 to get out of reset.

Addresses—Port 0 (0xE001 2024), Port 1 (0xE001 2224)

14:12

11:10

CRSDELAY[2:0]

RSVD

State on RST

(0)

Reserved.

CRSDELAY[2]

CRSDELAY[1]

CRSDELAY[0]

(0)

10 Mbits/s mode.

Bit #

Name

Bit #

31:15

14:12

31:15

RSVD

Name

RSVD

9

8

7

6

5:0

RXDVAV

XMTE

Description

RCVE

DAP

RSVD

(1)

(0)

CRS delay.

In 10 Mbits/s mode,

CRS

is never delayed, so these bits are ignored in

In 100 Mbits/s mode, these bits are used to set a delay for the start of

preamble regeneration from the receipt of

CRS

from the PHY. This regis-

ter is typically programmed to a value other than the default (100) when

the repeater is connected to a T4 PHY. Due to the variability of T4 receiv-

ers and the requirement for accurate preamble generation on the trans-

mit side, this value sets up a count to adjust the start of preamble. The

contents of this register will be a 3-bit binary value that represents the

number of additional

MSTCLK

cycles to wait after the assertion of

CRS

to begin preamble generation on the backplane (i.e., 000 = 0

MSTCLK

s,

111 = 7

MSTCLK

s).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8502 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8503 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8531A | T8531A/8532 Multichannel Programmable Codec Chip Set |

| T8531 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8532 | T8502 and T8503 Dual PCM Codecs with Filters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8302A | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

| T8302B | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

| T8302F | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

| T8303A | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

| T8303ABNAD | 制造商:Arcolectric 功能描述:1 Pole Miniature push button(with light) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。